Automating Design and Verification of Embedded Systems Using Metamodeling and Code Generation Techniques

What is Metamodeling and Code Generation All About

Wolfgang Ecker & Michael Velten, Infineon

SYSTEMS INITIATIVE

# **Tutorial**

Automating Design and Verification of Embedded Systems Using Metamodeling and Code Generation Techniques

Wolfgang Ecker, Michael Velten - Infineon Technologies AG Rainer Findenig - Intel Corp. Daniel Müller-Gritschneder - Technical University of Munich Wolfgang Mueller – Heinz-Nixdorf Institut University of Paderborn

#### Outline and Schedule

What is Metamodeling and Code Generation All About

- Motivation, Technology and Terminology

- Well known Metamodels in EDA and Design

- UML/SysML

- IP-XACT

Coffee Break

Metamodeling in Action using Eclipse Modeling Framework

- Generate a code generation framework for IP-XACT

- Specify an IP-XACT model and generate code out of it

## **Motivation** for Using Meta-Modeling and Code Generation

Infineon Designers on Single Design Tasks

- Up to 95% reduction in SW header generation

- Savings of about 1PY / year through test file generation

- Savings of about 4-5PYs / year through efficient solutions handling test programs

- Infineon Designers on Full Chip Implementation

- 60% effort reduction and 2 months project time savings from specification to implementation

- 80% code of digital design part generated

MetaCase

Up-to 20x speed and productivity improvement in using MetaEdit (A Metamodeling Framework) for SW Development

### **A Well Known Scenario:** Scripts Supporting Design Productivity

<u>Problems:</u> Starts easy, gets more and more complex (and harder to maintain) and ends up in spaghetti-code due to ...

- increasing requirements,

- more output formats and alternatives, and

- more complicated import formats

The good aspect: Content is automatically copied, code is generated, and nothing is retyped

2015-03-02

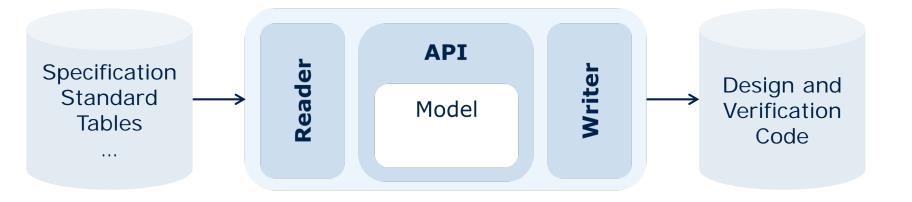

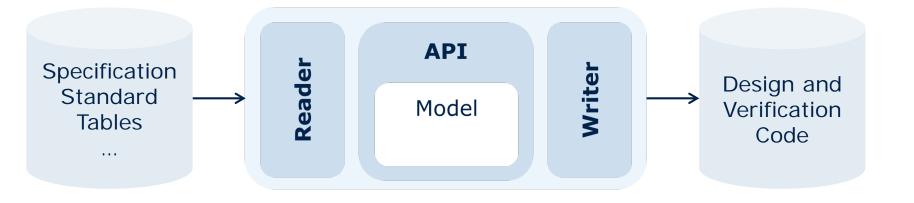

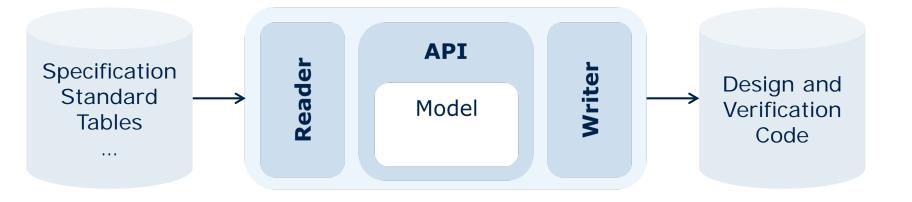

#### 1<sup>st</sup> Improvement: Model-View Separation

Model-View Separation is a good, well-known and powerful SW Concept (Pattern)

MyScript is separated in 3 pieces

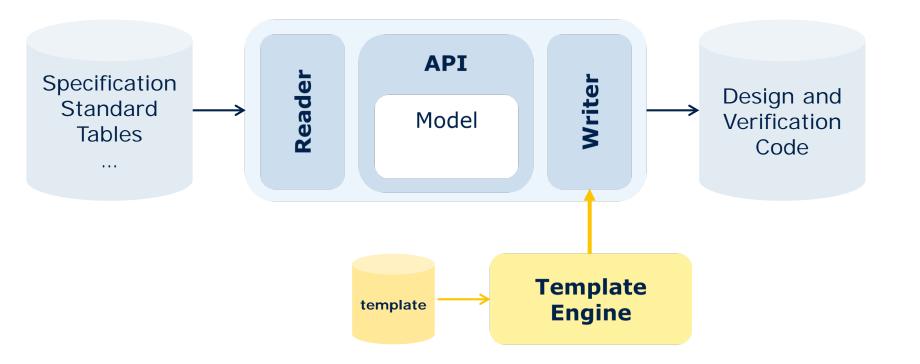

An <u>API</u> that controls access to structured data called **Model**

- A <u>Reader</u> that takes abstract data and fills the model

- A <u>Writer</u> that extracts data from and generates code

#### 1<sup>st</sup> Improvement: Model-View Separation

#### <u>Benefit</u>

- New and more complicated input and output formats can be supported by local changes

- Existing parts can be used further on

#### Model-View Separation Reader

Tasks of a reader:

Parse a description that is more abstract than the target code (e.g. specification items, domain specific languages)

Building blocks of a reader:

- Libraries as XML Readers, document readers as MS-Office or OpenOffice readers, PDF-parser, ...

- HDL Readers (Verific), compilers with open API (e.g. clang)

- Generated Parsers (e.g. via ANTLR) ...

2015-03-02

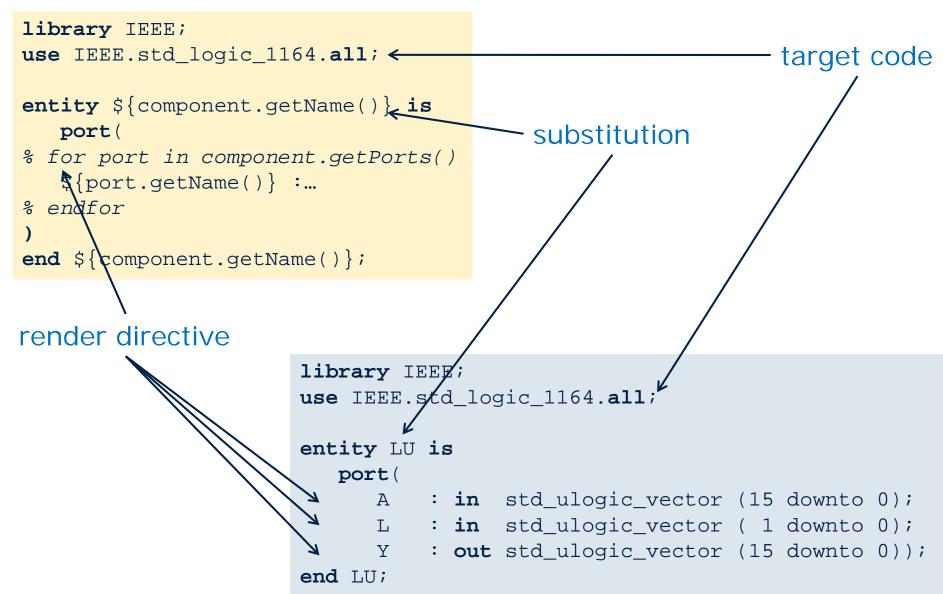

Different approaches to implement writers:

Sequence of prints, each taking values from the model

print("entity %s is\n", model.name);

- Systematic model traversal (mostly breath first or depth first) and registration of prints as actions when entering/leaving a node

- Template Engines, e.g.: FreeMarker (Java, EMF), Mako (Python, used by IFX), xsd: template as part of XSLT

### Model-View Separation Templates (Mako)

#### Model-View Separation Template Engines

A Template Engine translates visible or under the hood a template to a writer and then controls execution of the writer

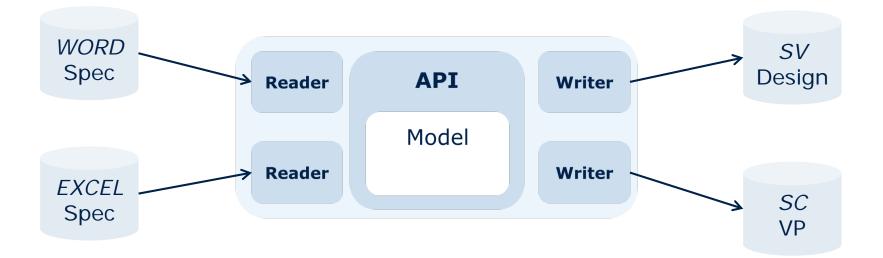

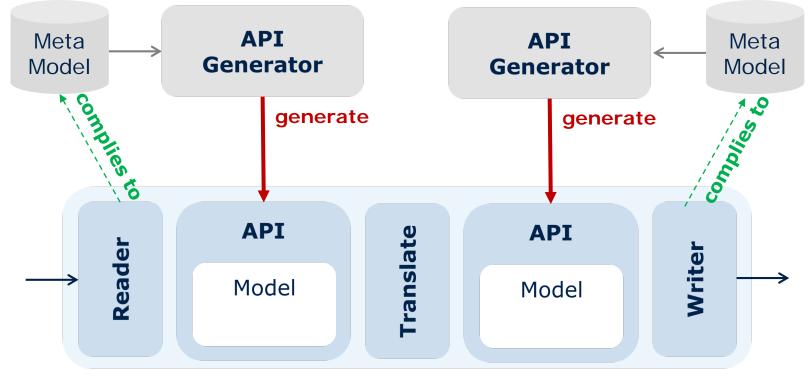

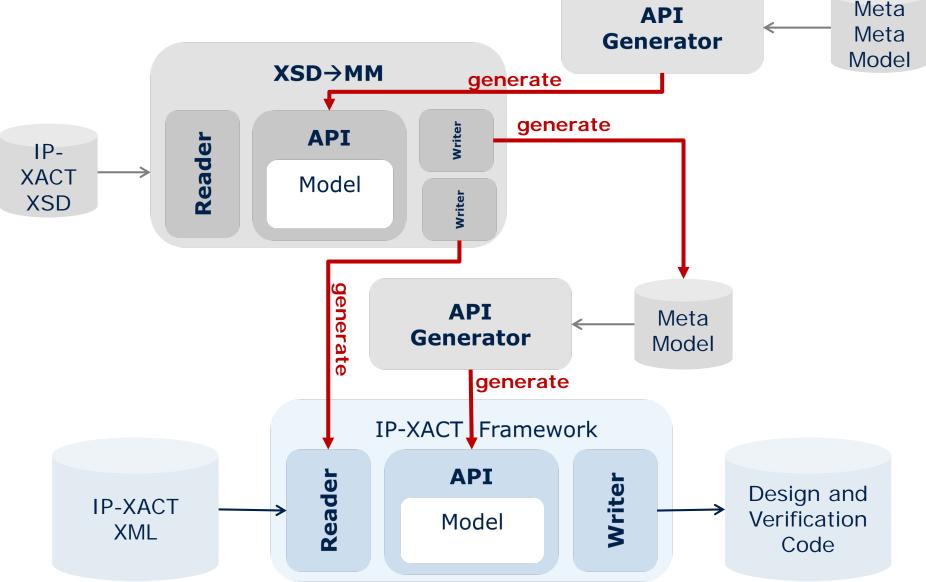

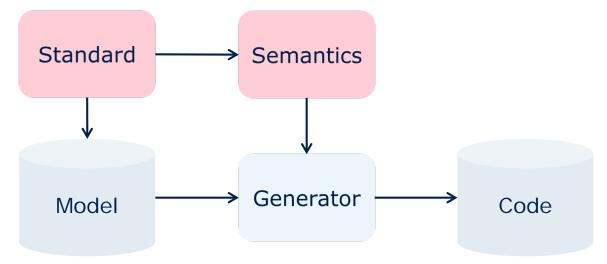

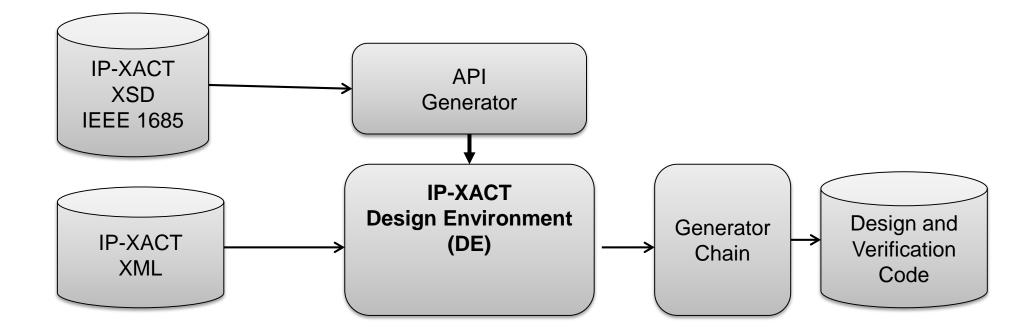

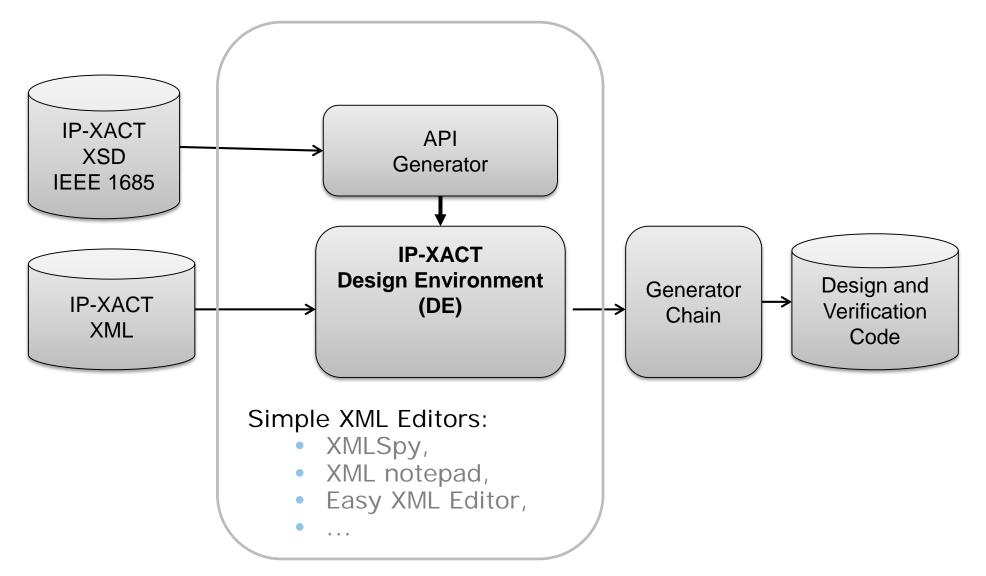

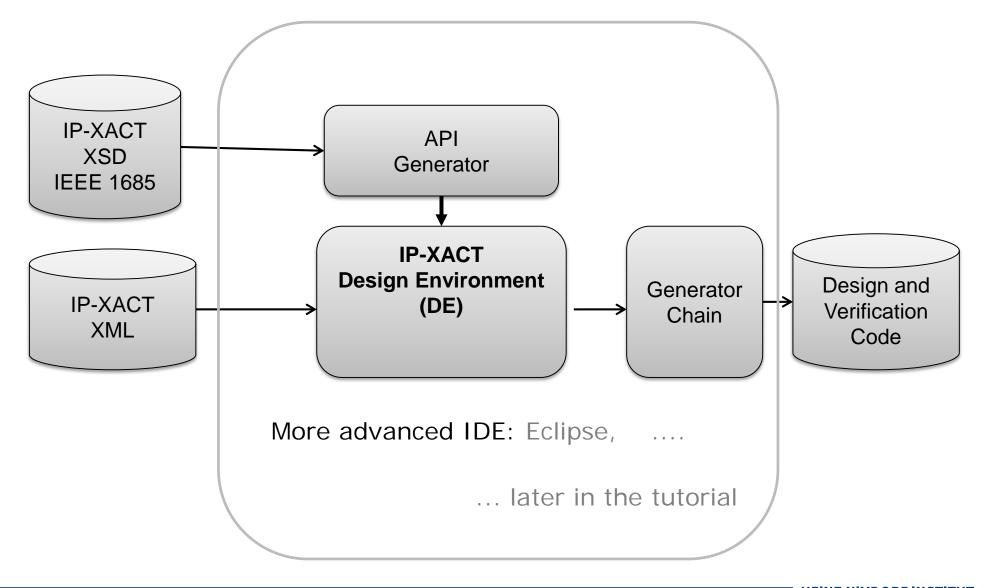

## 2<sup>nd</sup> Improvement: Generation of Tool's Code from Metamodel

Structure definition by Metamodel:

- Reader / Writer has to comply to Metamodel's structure and types

- API can be generated

- API generator offers to be structured similarly:

- Reader, API (Model), Writer

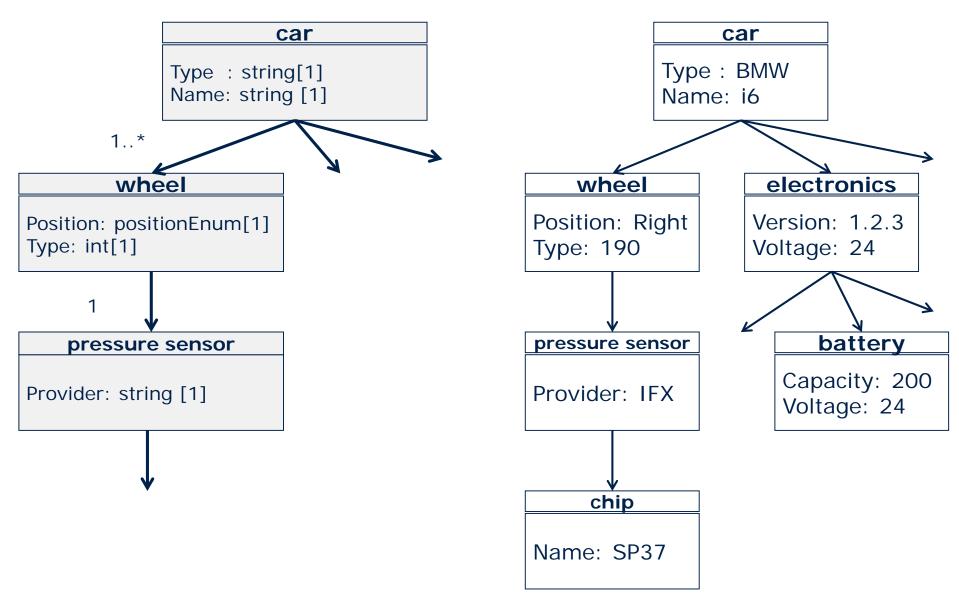

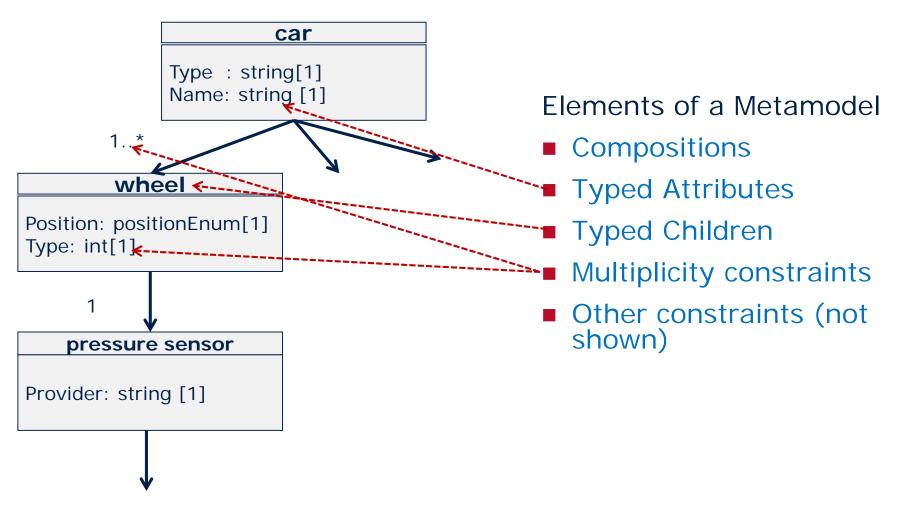

### Model-View Separation A Core Model of a Metamodel

- What is a simple Metamodel composed of

- Composite Data

- Typed or Un-Typed Attributes

- Typed or Un-Typed Children

- Typed or Un-Typed Links

- Optional multiplicity or other constraints

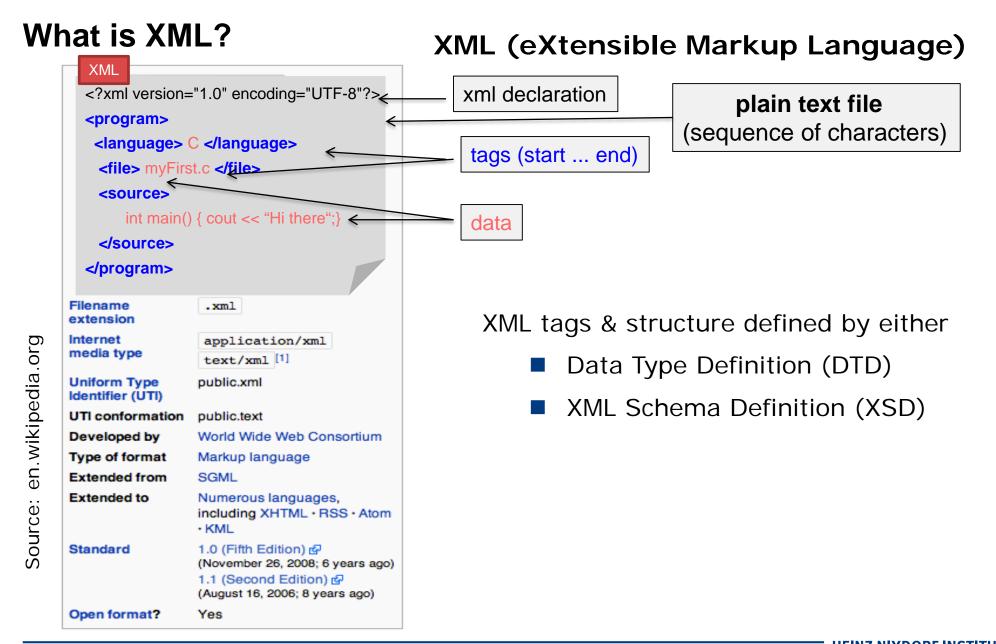

There are several techniques out that support Metamodeling and Code Generation. Examples are:

- XML with XSD (XML Schema)

- UML based on (E)MOF

- EMF based on (E)CORE

- METAGEN based on MMANALYZE (IFX-proprietary)

The elements of a Metamodel are defined in a so called Meta-Metamodel (we will see its usefulness later)

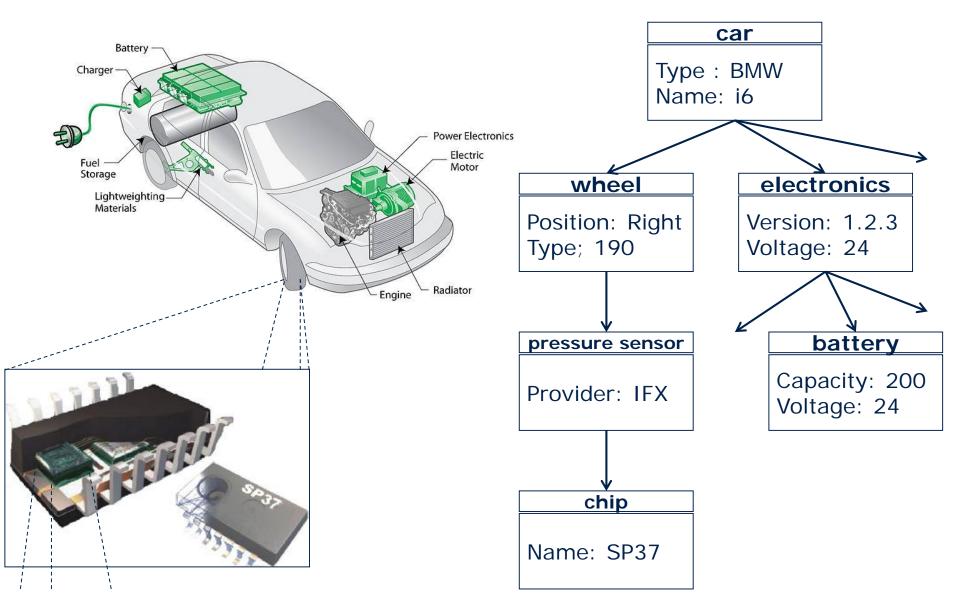

### Metamodeling Technology: Modeling Is About Structuring and Formalizing Things

#### Metamodeling Technology: <u>Metamodeling</u> Is About Structuring and Formalizing Models

#### **Metamodeling Technology:** <u>Metamodeling</u> Is About Structuring and Formalizing Models

## Some Known Metamodels UML and IP-XACT

UNIFIED MODELING LANGUAGE Details in 2<sup>nd</sup> part of the tutorial

- Graphical formalism (primarily) to describe/model SW Systems

- Formalisms describe structure, behavior and interaction

- Examples are class diagrams, object diagrams, state diagrams, activity diagrams

- UML is based on a superstructure (MOF, EMOF) that defines the formalism

- OCL (object constraint language) is used to defined further constraints and MARTE support embedded

Stereotypes as SYSTEMS SYSTEMS

Systems systemš

- Defines data that support <u>automation in IP-integration</u>. Includes

- Busses, components with their registers, connectivity

- Does not model IP-Internals

#### Metamodeling Technique Additional Features of a Core Model

Wide range of products (IFX Examples Shown) require <u>flexibility in</u> <u>Metamodeling</u>

- Extendibility

- Constraints

- Interaction

- Composition

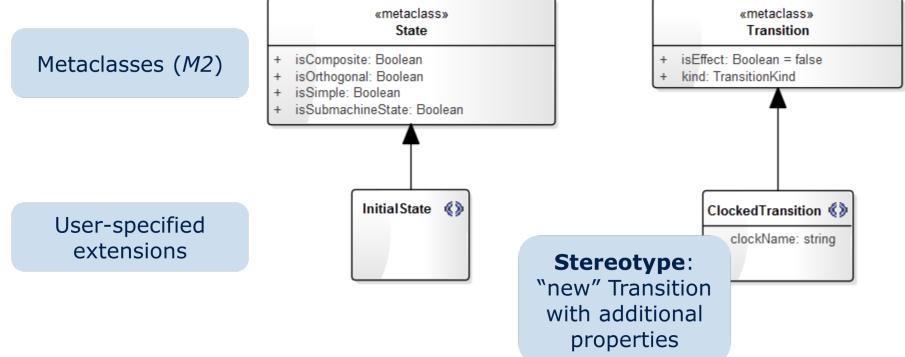

#### Metamodeling Technique Extendibility and Constraints

#### Examples

- Analog types and their properties

- Register protection mechanisms

- Clocked State Diagrams

#### Constructs for extendibility in different notations

- Supported e.g. by inheritance in core model

- UML uses profiles or OCL

- XML provides restrictions and complex datatypes

## Metamodeling Technique Interaction and Composition

Examples

- Registers or State diagrams manipulate ports

- Constructs for extendibility

- Link mechanism e.g. XML XPATH

- Model-to-Model translation

2015-03-02

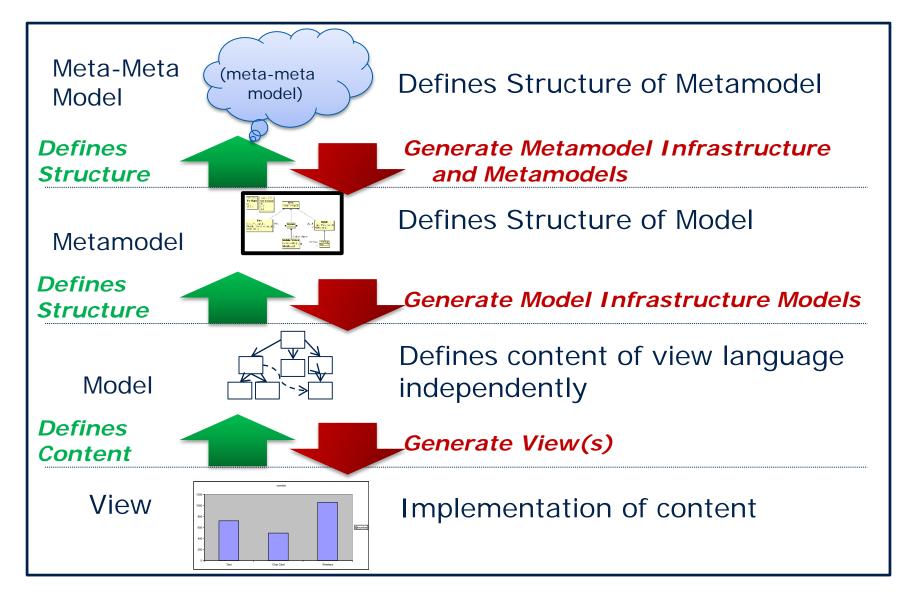

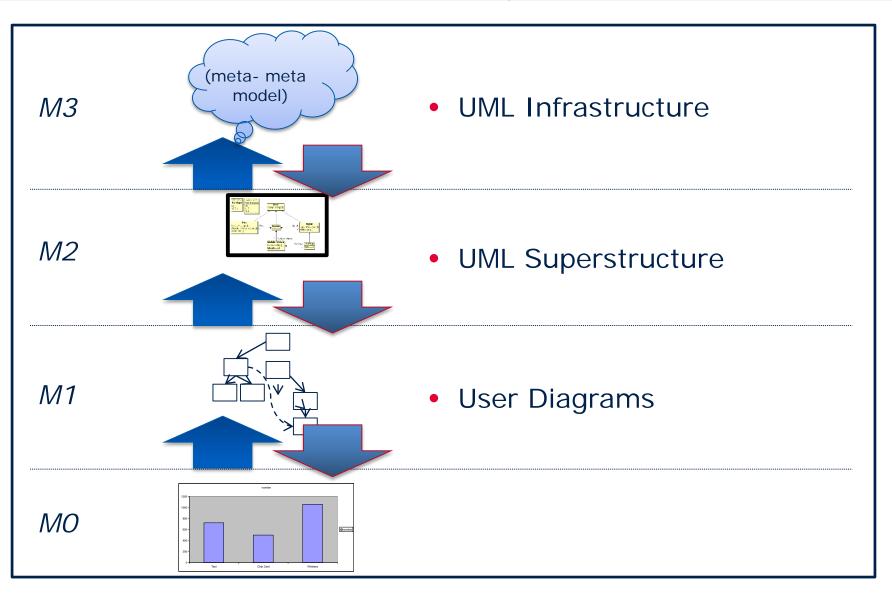

## Metamodeling Technology Layers in Structuring Data

## Meta-Metamodel: Is About Structuring Metamodels, i.e. Metamodel of Metamodel

nfineon

Copyright © Infineon Technologies AG 2015. All rights reserved.

## Meta-Metamodel: Is About Structuring Metamodels, i.e. Metamodel of Metamodel

## Shown in 3<sup>rd</sup> part of the tutorial building an IP-XACT to target code translation

#### It's All About Structuring Summary and Retrospect

All is not new! Metamodeling has a >25-year history

- Formally called Express Information Model

- Further developed in Jessi Common Framework Initiative (CFI)

- Formal foundation for EDIF (Electronic Design Interchange Format)

- Meta-Modeling: Performance and Information Modeling Current Issues in Electronic Modeling (6), Springer, ISBN 9780792396871

- Meta-Modeling: Current Issues in Electronic Modeling (6), ISBN 9780792396871

#### It's All About Structuring Summary and Outline

Metamodeling and Code generation is

- an industry proven technology to efficiently build domain/problem specific tools following a specific structure

- Modeling in the context of Metamodeling is about

- structuring things in a design context

- Metamodeling is about

- Structuring Models

SYSTEMS INITIATIVE

Automating Design and Verification of Embedded Systems Using Metamodeling and Code Generation Techniques

Well known Metamodels in EDA and Design: UML/SysML

Wolfgang Ecker, Infineon; Rainer Findenig, Intel

SYSTEMS INITIATIVE

#### The Unified Modeling Language (UML) is a generalpurpose modeling language in the field of software engineering, which is designed to provide a standard way to visualize the design of a system.

en.wikipedia.org

Software Centric

The Unified Modeling Language (UML) is a generalpurpose modeling language in the field of software engineering, which is designed to provide a standard way to visualize the design of a system.

en.wikipedia.org

#### The Unified Modeling Language (UML) is a generalpurpose modeling language in the field of software engineering, which is designed to provide a standard way to visualize the design of a system.

Standardized by the Object Management Group en.wikipedia.org

#### The Unified Modeling Language (UML) is a generalpurpose modeling language in the field of software engineering, which is designed to provide a standard way to visualize the design of a system.

Graphical Language en.wikipedia.org

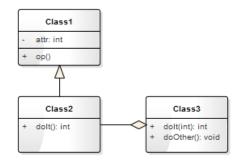

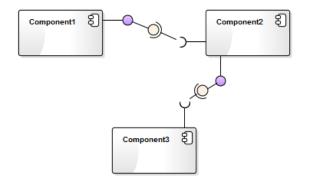

- Structural modeling:

- Class diagram

- Component diagram

- Deployment diagram

□ ...

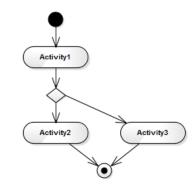

- Behavioral modeling:

- Activity diagram

- Sequence diagram

- State diagram

□ ...

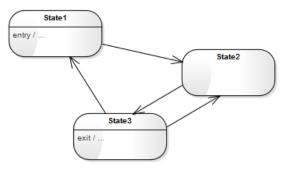

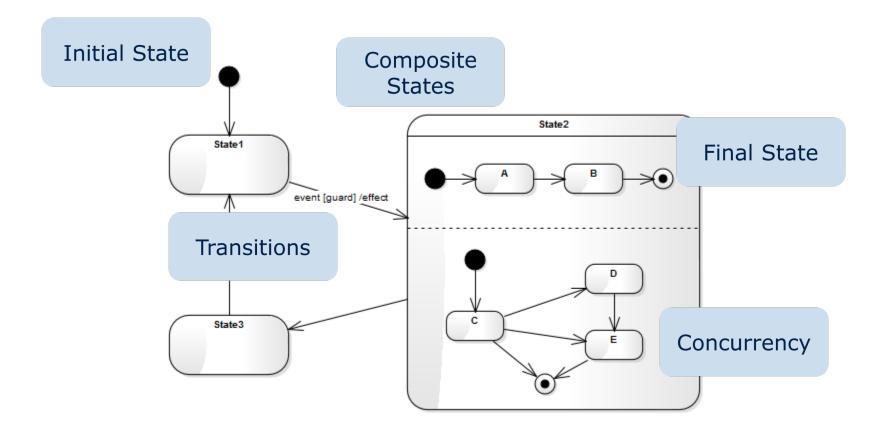

#### An Example: UML State Diagrams

#### UML?

- Graphical Language

- Easy to read

- □ Easy to write?

- Semantics

- Not formally defined; software oriented

- □ Given to your model as part of the code generation

- Tool support is critical!

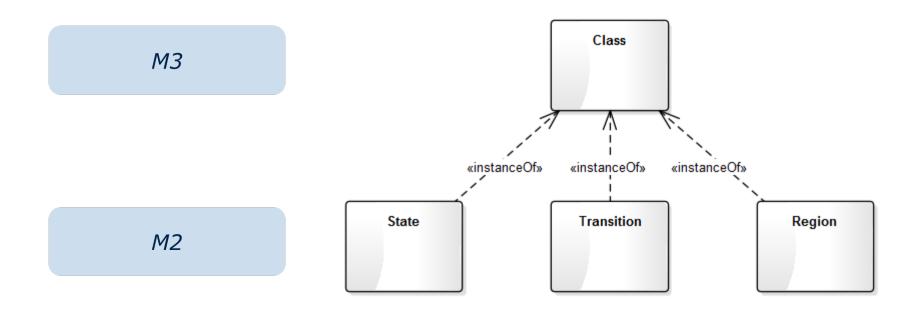

#### UML: The Spirit of Metamodeling

## **Extending UML: Profiles**

Extension mechanism for customizing UML

- Light-weight, easy

- Strictly additive, no fundamental changes

Copyright © Infineon Technologies AG 2015. All rights reserved

## Extending UML: MOF – Meta-Object Facility

- UML itself is defined in the MOF

- Allows defining completely new Metamodels

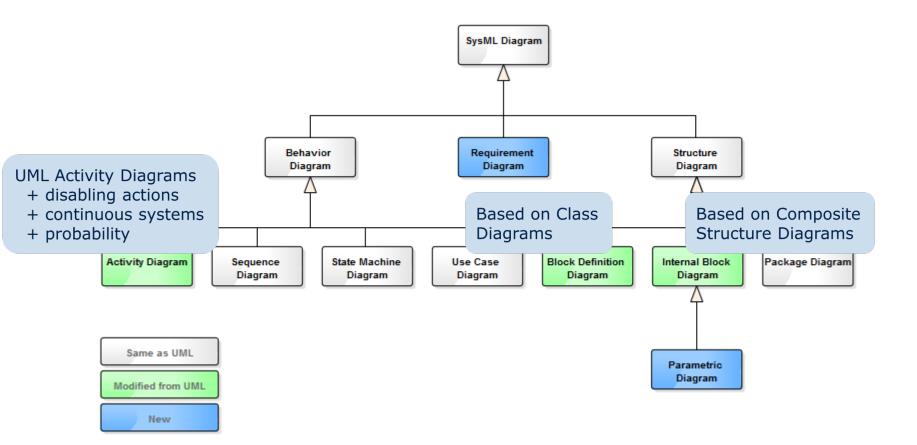

#### SysML

- Extended subset of UML

- Defined using profiles

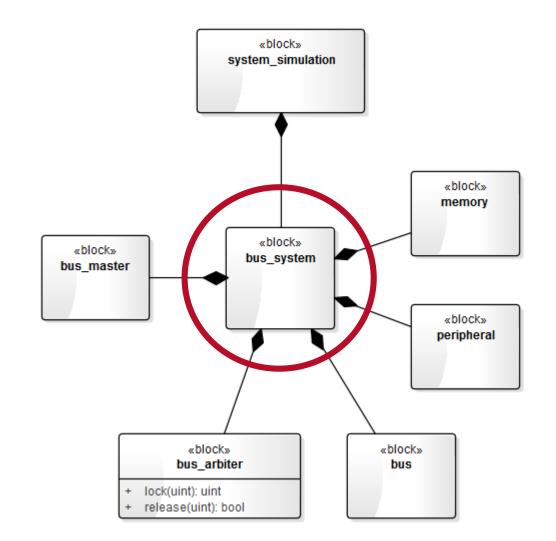

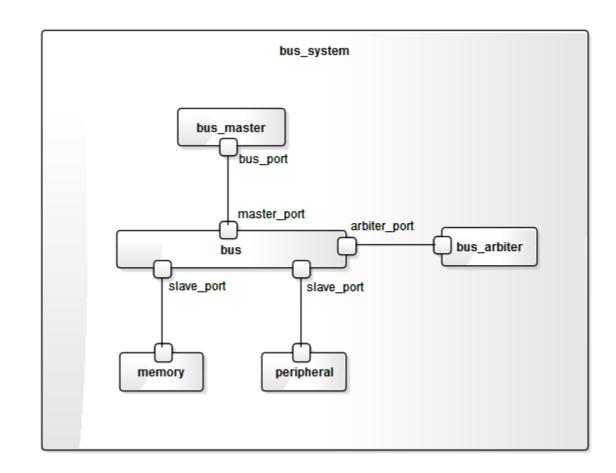

## SysML: Block Definition Diagram

## SysML: Internal Block Diagram

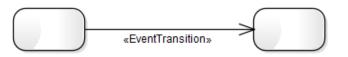

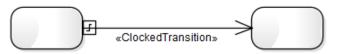

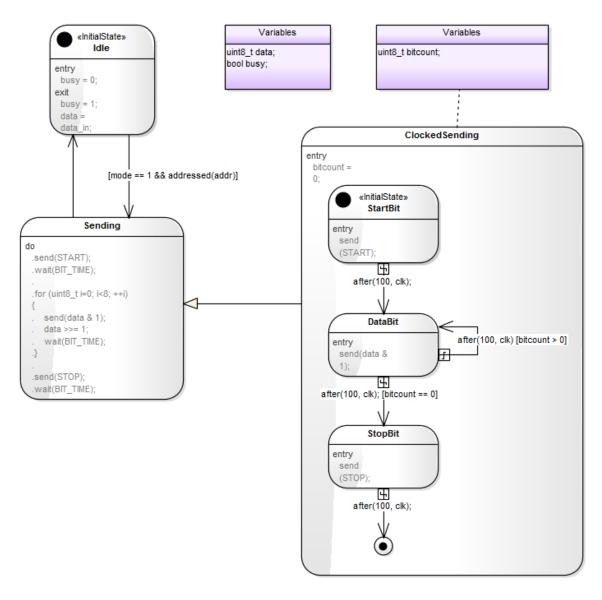

## UML State Diagrams for Different Abstraction Levels

UML Profile

- Event-driven transitions:

- Derived from time, transactions, or other internal/external events

- □ Clock-driven transitions:

- Derived from an internal clock

- Can use guards for specifying timeouts

#### UML State Diagrams for Different Abstraction Levels

UML Profile

Initial states to conform with hardware reset semantics

#### □ Global and local variables

| Variables       |

|-----------------|

| bool busy;      |

| uint8_t data;   |

| uint32_t count; |

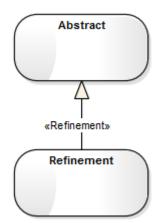

## UML State Diagrams for Different Abstraction Levels

- UML Profile

- □ Link to external interface definition

- Including selection of desired abstraction level

Refinement between states and transitions

## Example: SIF

Copyright © Infineon Technologies AG 2015. All rights reserved.

SYSTEMS INITIATIVE

Automating Design and Verification of Embedded Systems Using Metamodeling and Code Generation Techniques

#### Well known Metamodels in EDA and Design: IP-XACT

Wolfgang Mueller, Heinz Nixdorf Institute; Daniel Müller-Gritschneder, Technical University of Munich

SYSTEMS INITIATIVE

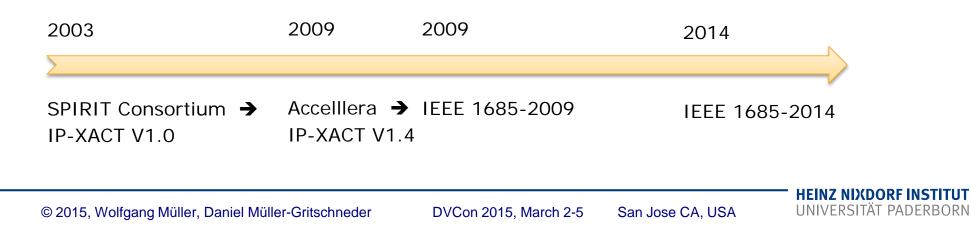

## **IP-XACT** Overview

#### **IP-XACT IEEE 1685**

Standard Structure for Packaging, Integrating, and Reusing IP within Tool Flows

- design-language neutral design exchange format

- Electronic System Level IP components (ESL netlists + Code Generation)

- IP component attributes: interfaces, signals, parameters, memory maps, registers, ...

- IP component processing information: generators and file sets

for assembly, simulation, synthesis, test insertion,

Related Spirit/Accellera standard:

2

SystemRDL (Register Description Language) for HW/SW interface components, 2009

## **IP-XACT** Overview

#### **IP-XACT IEEE 1685**

Standard Structure for Packaging, Integrating, and Reusing IP within Tool Flows

DVCon 2015, March 2-5

San Jose CA, USA

HEINZ NIXDORF INSTITUT UNIVERSITÄT PADERBORN

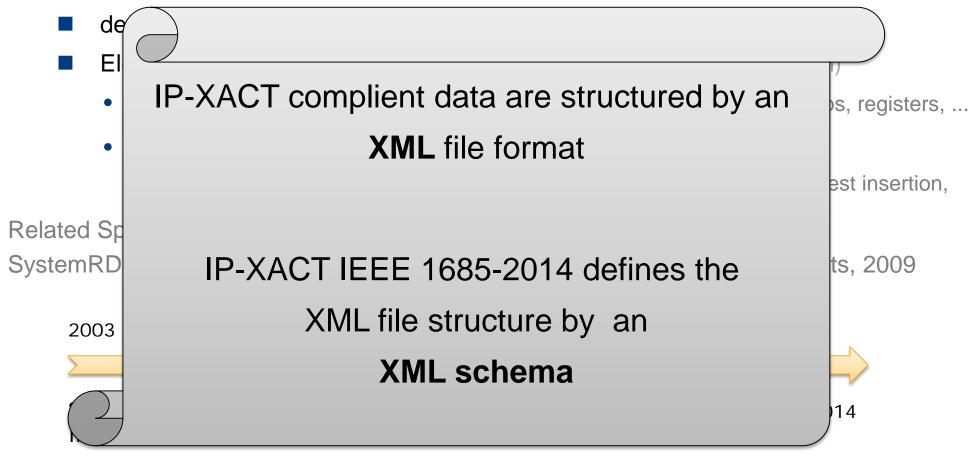

## What is XSD?

#### XML Schema Definition (XSD)

- defines structure for xml file

- developed by World Wide Web Consort.

- file extension: .xsd

- compares to UML Class Diagrams

- note: xsd is defined in xml format!

#### XSD

<?xml version="1.0"?> <xs:schema xmlns:xs="http://www.w3.org/2001/XMLSchema">

```

<xs:element name="program">

<xs:complexType>

```

```

<xs:sequence>

```

```

<xs:element name="language" type="xs:string"/>

<xs:element name="file" type="xs:string"/>

<xs:element name="source" type="xs:string"/>

```

```

</xs:sequence>

```

```

</xs:complexType>

```

</xs:element>

</xs:schema>

#### **Recall: Metamodel Defines IP-XACT Structure**

**HEINZ NIXDORF INSTITUT**

DVCon 2015, March 2-5

#### **IP-XACT IEEE 1685-2014**

| IEEE STANDARDS ASSOCIATION                                                                                          | <b>\$IEEE</b> |  |

|---------------------------------------------------------------------------------------------------------------------|---------------|--|

| IEEE Standard for IP-XACT,<br>Standard Structure for Packaging,<br>Integrating, and Reusing IP within<br>Tool Flows |               |  |

|                                                                                                                     |               |  |

| IEEE Computer Society                                                                                               |               |  |

| Sponsored by the<br>Design Automation Standards Committee                                                           |               |  |

IEEE 3 Park Avenue New York, NY 10016-5997 USA

IEEE Std 1685<sup>™</sup>-2014 (Revision of IEEE Std 1685-2009)

#### Contents

- 1. Overview

- 2. Normative references

- 3. Definitions, acronyms, abbreviations

- 4. Interoperability use model

- 5. Interface definition descriptions

- 6. Component descriptions

- 7. Design descriptions

- 8. Abstractor descriptions

- 9. Generator chain descriptions

- 10. Design configuration descriptions

- 11. Catalog descriptions

- 12. Addressing

- 13. Data visibility

- Annex A Annex I:

Bibliography, Semantic consistency rules, Common elements and concepts, Types, SystemVerilog expressions, Tight generator interface, External bus with an internal/digital interface, Bridges & channels, Examples

San Jose CA, USA

#### **IP-XACT IEEE 1685-2014**

|                                                                                                                                        | Contents                                                                                                                                                                                                                          |  |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IEEE STANDARDS ASSOCIATION                                                                                                             | 1. Overview                                                                                                                                                                                                                       |  |

|                                                                                                                                        | 2. Normative references                                                                                                                                                                                                           |  |

|                                                                                                                                        | 3. Definitions, acronyms, abbreviations                                                                                                                                                                                           |  |

| IEEE Standard for IP-XACT,<br>Standard Structure for Packaging,                                                                        | 4. Interoperability use model                                                                                                                                                                                                     |  |

| Integrating, and Reusing IP within                                                                                                     | 5. Interface definition descriptions                                                                                                                                                                                              |  |

| Tool Flows                                                                                                                             | 6. Component descriptions                                                                                                                                                                                                         |  |

|                                                                                                                                        | 7. Design descriptions                                                                                                                                                                                                            |  |

|                                                                                                                                        | 8. Abstractor descriptions                                                                                                                                                                                                        |  |

|                                                                                                                                        | 9. Generator chain descriptions                                                                                                                                                                                                   |  |

|                                                                                                                                        | 10. Design configuration descriptions                                                                                                                                                                                             |  |

| IEEE Computer Society                                                                                                                  | 11. Catalog descriptions                                                                                                                                                                                                          |  |

| Sponsored by the                                                                                                                       | 12. Addressing                                                                                                                                                                                                                    |  |

| Design Automation Standards Committee                                                                                                  | 13. Data visibility                                                                                                                                                                                                               |  |

|                                                                                                                                        | Annex A – Annex I:                                                                                                                                                                                                                |  |

| IEEE IEEE Std 1685 <sup>m</sup> -2014<br>3 Park Avenue (Revision of<br>New York, NY 10016-5997 (Revision of<br>USA IEEE Std 1685-2009) | Bibliography, Semantic consistency rules,<br>Common elements and concepts, Types,<br>SystemVerilog expressions, Tight generator<br>interface, External bus with an<br>internal/digital interface, Bridges &<br>channels, Examples |  |

**HEINZ NIXDORF INSTITUT**

UNIVERSITÄT PADERBORN

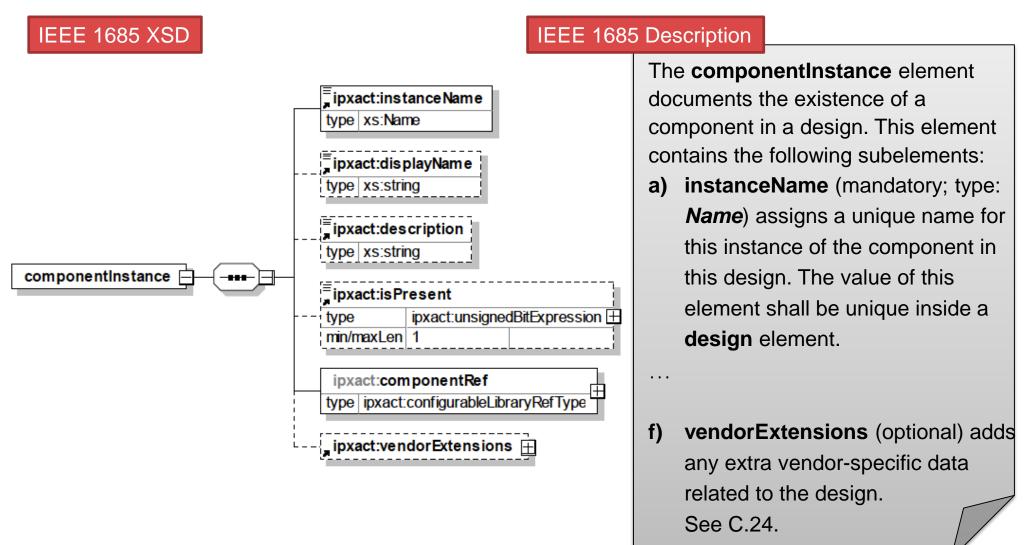

### **IP-XACT Example: componentInstance**

DVCon 2015, March 2-5

HEINZ NIXDORF INSTITUT UNIVERSITÄT PADERBORN

12 © 2015, Wolfgang Müller, Daniel Müller-Gritschneder

DVCon 2015, March 2-5

San Jose CA, USA

|                                            | Some IP-XACT Objects                                                     |  |  |  |  |  |

|--------------------------------------------|--------------------------------------------------------------------------|--|--|--|--|--|

| Design                                     | Configures component instances &                                         |  |  |  |  |  |

|                                            | interconnections (Netlist)                                               |  |  |  |  |  |

| Component                                  | Describes IP's interfaces: Ports,                                        |  |  |  |  |  |

|                                            | bus interfaces with bus and abstraction type,                            |  |  |  |  |  |

|                                            | address spaces, memory maps, registers,                                  |  |  |  |  |  |

|                                            | parameters, views, file sets,                                            |  |  |  |  |  |

|                                            | IP stored in physical file as Verilog, VHDL,                             |  |  |  |  |  |

| <b>Bus Definition</b>                      | on describes bus protocol                                                |  |  |  |  |  |

| AbstractionDefinition describes bus on one |                                                                          |  |  |  |  |  |

|                                            | abstraction layer e.g. RTL, TLM                                          |  |  |  |  |  |

|                                            | done by unique IP-XACT VLNV identification (Vendor Library Name Version) |  |  |  |  |  |

|                                            |                                                                          |  |  |  |  |  |

DVCon 2015, March 2-5 Sa

14 © 2015, Wolfgang Müller, Daniel Müller-Gritschneder

DVCon 2015, March 2-5

San Jose CA, USA

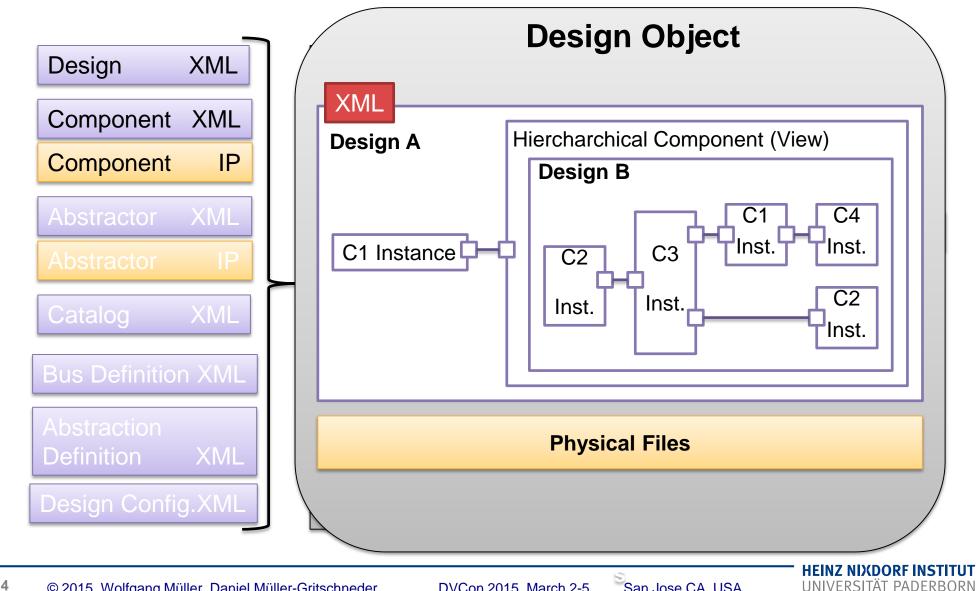

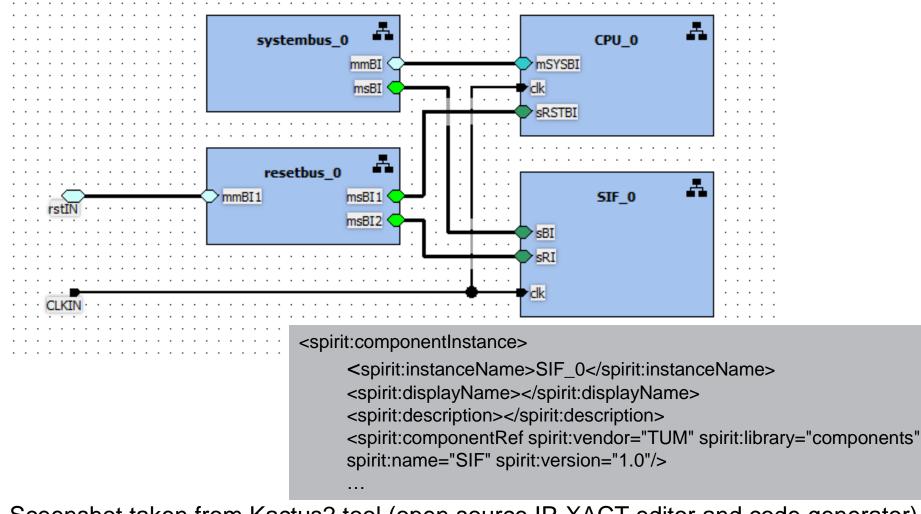

## **IP-XACT Design Example**

Design with four components: CPU, Serial Interface (SIF), two buses (system, reset)

Sceenshot taken from Kactus2 tool (open source IP-XACT editor and code generator)

DVCon 2015, March 2-5 San Jose CA, USA

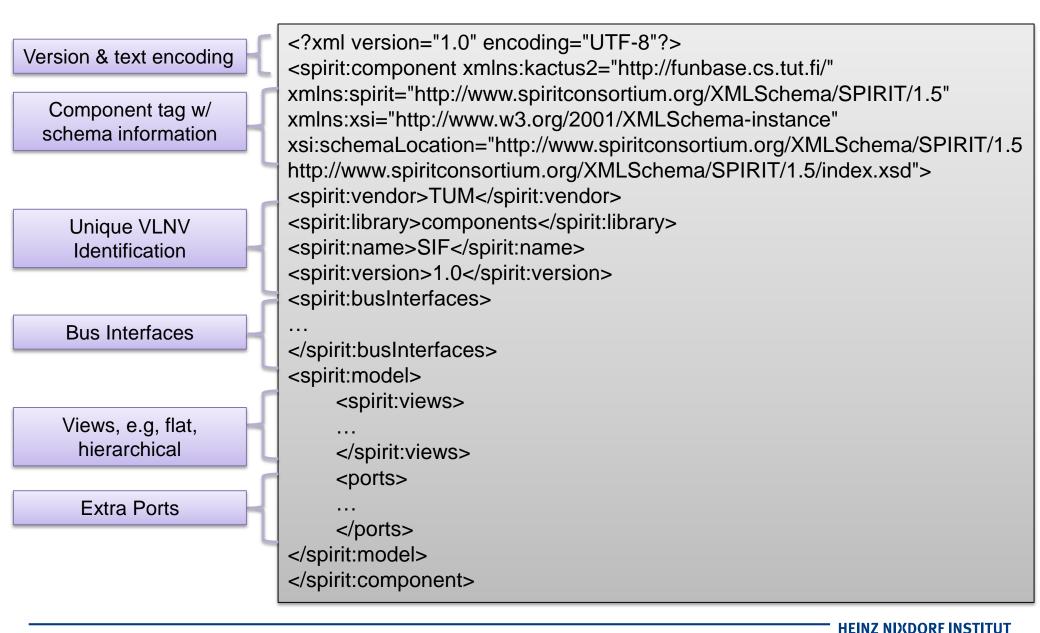

# **IP-XACT Component Example: SIF**

DVCon 2015, March 2-5

San Jose CA, USA

UNIVERSITÄT PADERBORN

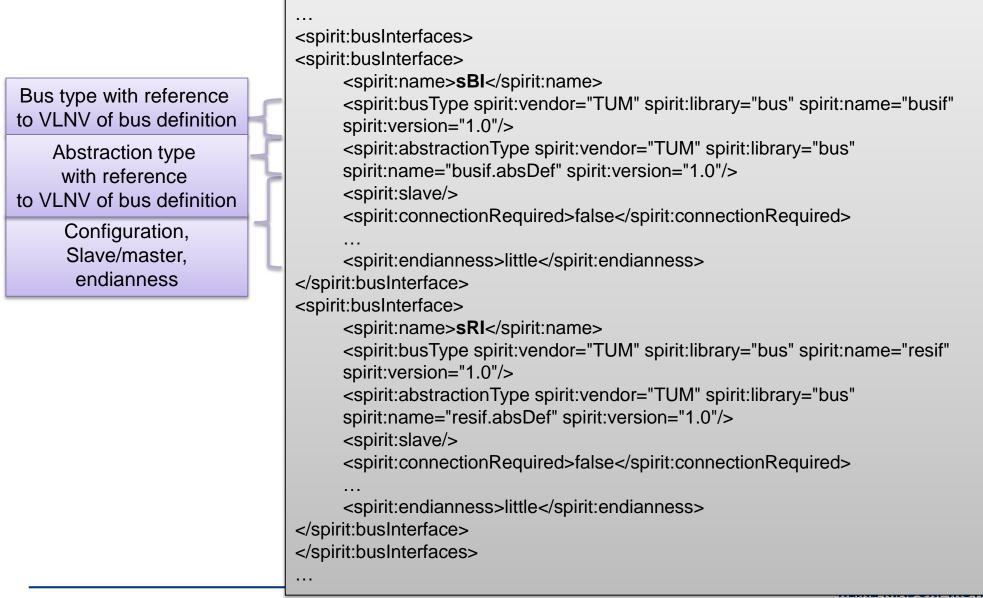

## **IP-XACT Component Example: SIF - Bus Interfaces**

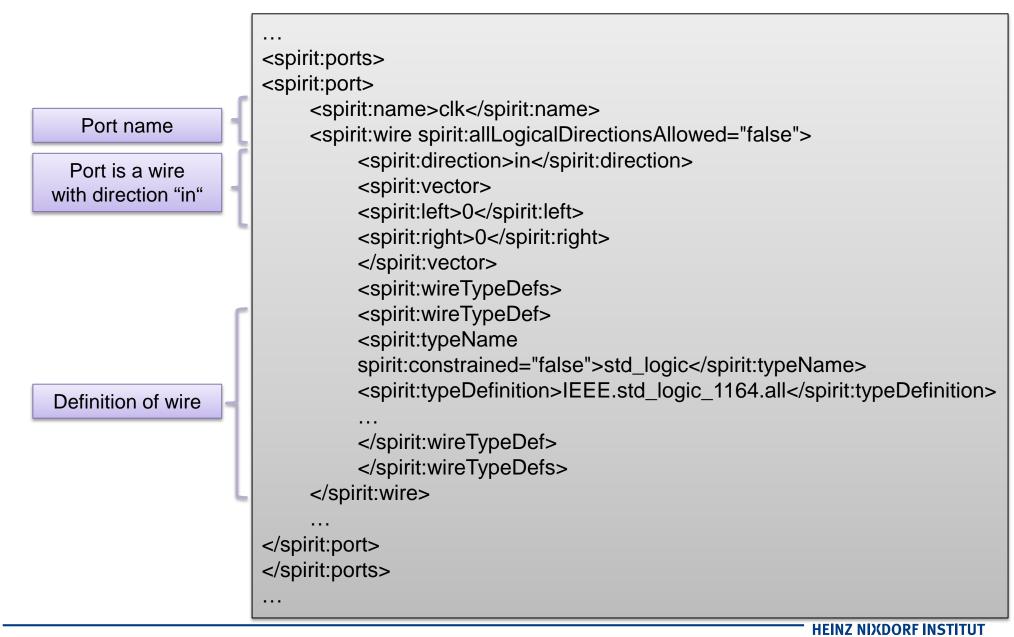

### **IP-XACT Component Example: SIF - Ports**

DVCon 2015, March 2-5

San Jose CA, USA

UNIVERSITÄT PADERBORN

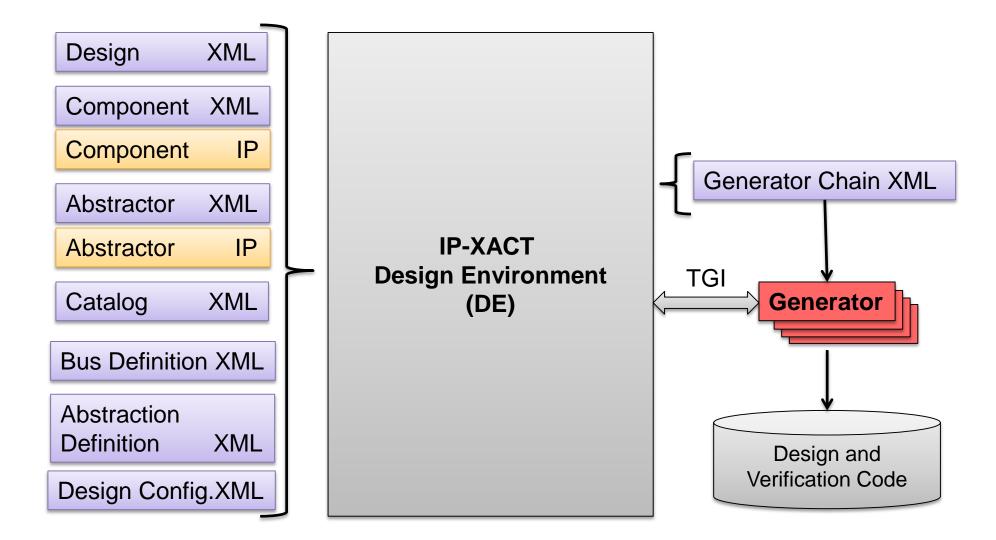

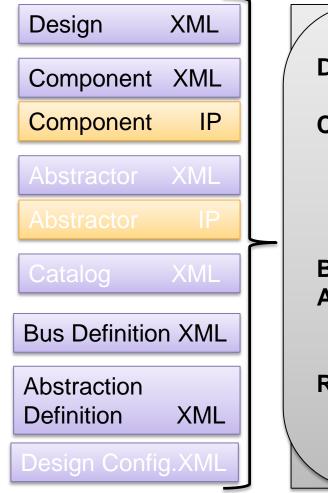

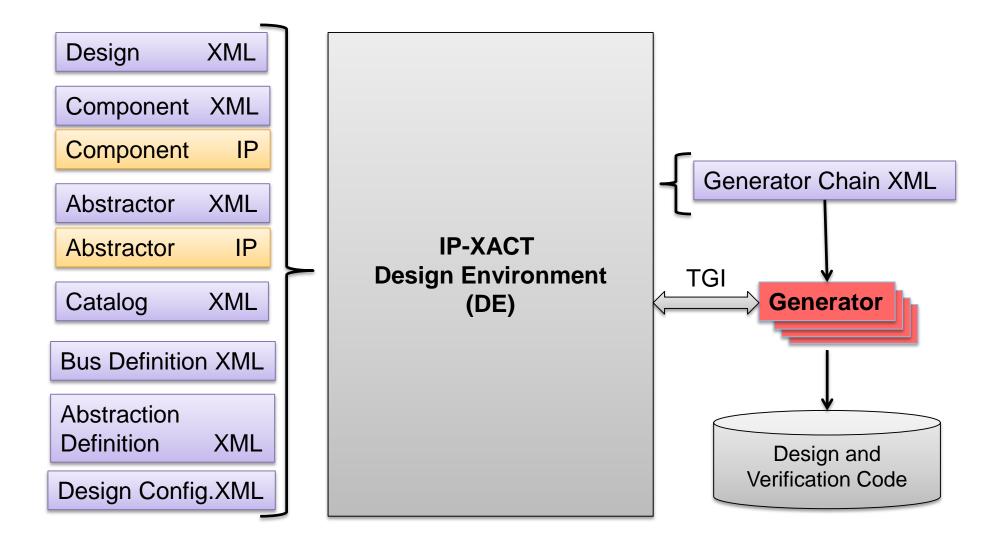

| Design<br>Component | XML   |                      | Additional                                              |

|---------------------|-------|----------------------|---------------------------------------------------------|

| Component           | IP    | Abstractor           | converter between two bus interfaces of two abstraction |

| Abstractor          | XML   |                      | types                                                   |

| Abstractor          | IP    | Catalog              | mapping of XP-XACT VLNV                                 |

| Catalog             | XML   | Catalog              | (Vendor Library Name Version)                           |

| Bus Definitio       | n XML |                      | to physical file defining the object                    |

| Abstraction         |       |                      |                                                         |

| Definition          | XML   | Design Configuration | additional information for                              |

| Design Confi        | g.XML |                      | design / generator                                      |

DVCon 2015, March 2-5

**HEINZ NIXDORF INSTITUT**

UNIVERSITÄT PADERBORN

HEINZ NIXDORF INSTITUT UNIVERSITÄT PADERBORN

20 © 2015, Wolfgang Müller, Daniel Müller-Gritschneder

DVCon 2015, March 2-5

San Jose CA, USA

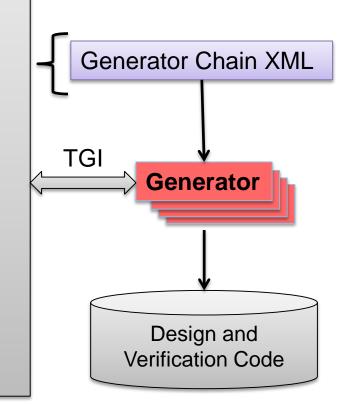

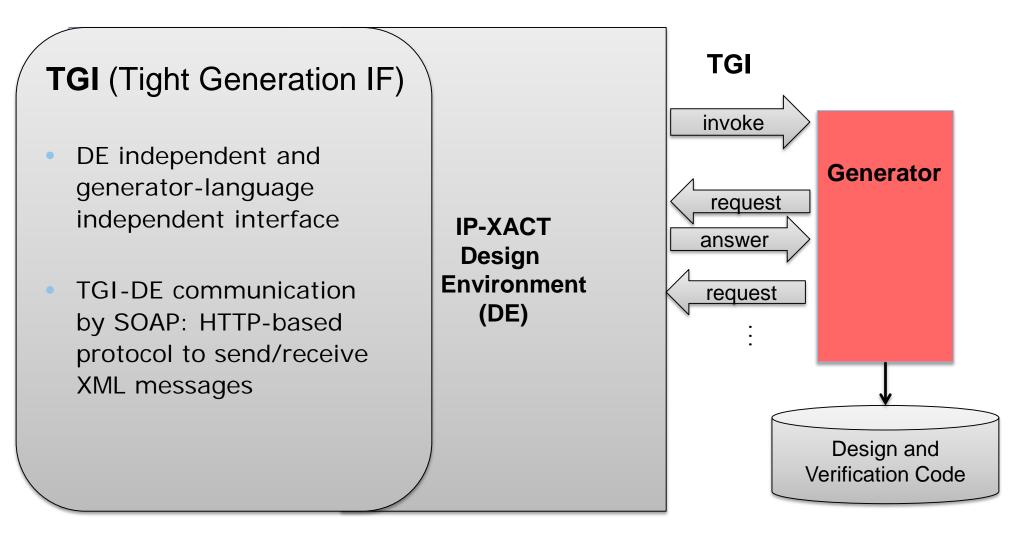

### Generator

- program module processes IP-XACT XML and generates code

- Implementation can be in any language

- XSLT (eXt. Stylesheet Language Transform.)

language: XML → other presentations

- scripting language like Tcl, Python

- programming language like Java, C++

uses TGI (Tight Generation Interface) to access IP-XACT models

San Jose CA, USA

DVCon 2015, March 2-5

San Jose CA, USA

#### HEINZ NIXDORF INSTITUT UNIVERSITÄT PADERBORN

SYSTEMS INITIATIVE