# SystemRDL 2.0 Register Description Language

January 2018

Copyright © 2015 - 2018 Accellera. All rights reserved. **Abstract:** Information about the registers in a circuit design is required throughout its lifetime, from initial architectural specification, through creation of an HDL description, verification of the design, post-silicon testing, to deployment of the circuit. A consistent and accurate description of the registers is necessary so the registers specified by the architects and the registers programmed by the users of the final product are the same. SystemRDL is a language for describing registers in circuit designs. SystemRDL descriptions are used as inputs to software tools that generate circuit logic, test programs, printed documentation, and other register artifacts. Generating all of these from a single source ensures their consistency and accuracy. The description of a register may correspond to a register in an preexisting circuit design, or it can serve as an input to a synthesis tool that creates the register logic and access interfaces. A description captures the behavior of the individual registers, the organization of the registers into register files, and the allocation of addresses to registers. A variety of register behaviors can be described: simple storage elements, storage elements with special read/write behavior (e.g., 'write 1 to clear'), interrupts, and counters.

**Keywords:** hardware design, electronic design automation, SystemRDL, hierarchical register description, control and status registers, interrupt registers, counter registers, register synthesis, software generation, documentation generation, bus interface, memory, register addressing.

## Notices

Accellera Systems Initiative (Accellera) Standards documents are developed within Accellera and the Technical Committee of Accellera. Accellera develops its standards through a consensus development process, approved by its members and board of directors, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are members of Accellera and serve without compensation. While Accellera administers the process and establishes rules to promote fairness in the consensus development process, Accellera does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Use of an Accellera Standard is wholly voluntary. Accellera disclaims liability for any personal injury, property or other damage, of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon this, or any other Accellera Standard document.

Accellera does not warrant or represent the accuracy or content of the material contained herein, and expressly disclaims any express or implied warranty, including any implied warranty of merchantability or suitability for a specific purpose, or that the use of the material contained herein is free from patent infringement. Accellera Standards documents are supplied "AS IS."

The existence of an Accellera Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of an Accellera Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change due to developments in the state of the art and comments received from users of the standard. Every Accellera Standard is subjected to review periodically for revision and update. Users are cautioned to check to determine that they have the latest edition of any Accellera Standard.

In publishing and making this document available, Accellera is not suggesting or rendering professional or other services for, or on behalf of, any person or entity. Nor is Accellera undertaking to perform any duty owed by any other person or entity to another. Any person utilizing this, and any other Accellera Standards document, should rely upon the advice of a competent professional in determining the exercise of reasonable care in any given circumstances.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of Accellera, Accellera will initiate action to prepare appropriate responses. Since Accellera Standards represent a consensus of concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, Accellera and the members of its Technical Committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments for revision of Accellera Standards are welcome from any interested party, regardless of membership affiliation with Accellera. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Comments on standards and requests for interpretations should be addressed to:

> Accellera Systems Initiative. 8698 Elk Grove Bldv Suite 1, #114 Elk Grove, CA 95624 USA

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. Accellera shall not

be responsible for identifying patents for which a license may be required by an Accellera standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

Accellera is the sole entity that may authorize the use of Accellera-owned certification marks and/or trademarks to indicate compliance with the materials set forth herein.

Authorization to photocopy portions of any individual standard for internal or personal use must be granted by Accellera, provided that permission is obtained from and any required fee is paid to Accellera. To arrange for authorization please contact Lynn Garibaldi, Accellera Systems Initiative, 8698 Elk Grove Bldv Suite 1, #114, Elk Grove, CA 95624, phone (916) 670-1056, e-mail lynn@accellera.org. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained from Accellera.

Suggestions for improvements to the SystemRDL 2.0 Specification are welcome. They should be sent to the SystemRDL email reflector

systemrdl@lists.accellera.org

# Introduction

The SystemRDL language was specifically designed to describe and implement a wide variety of registers and memories. Using SystemRDL, developers can automatically generate and synchronize the register specification in hardware design, software development, verification, and documentation. The intent behind standardizing the language is to drastically reduce the development cycle for hardware designers, hardware verification engineers, software developers, and documentation developers.

SystemRDL is intended for

- RTL generation

- RTL verification

- SystemC generation

- Documentation

- Pass through material for other tools, e.g., debuggers

- Software development

# **Participants**

The following members took part in the SystemRDL Working Group (RDWG):

Miles McCoo, Intel Corporation, Chair RDWG Joe Daniels, Technical Editor

Allied Member: Michael Faust

Cisco Systems, Inc: Steve Russell, Somasundaram Arunachalam

Intel Corporation: Miles McCoo

Magillem Design Services: Guillaume Godet-Bar

NVIDIA Corporation: John Berendsen

Semifore, Inc: Richard Weber

# Contents

| 1. | Ove  | view                                  | 1  |

|----|------|---------------------------------------|----|

|    | 1.1  | Scope                                 | 1  |

|    | 1.1  | Purpose                               |    |

|    | 1.2  | Motivation                            |    |

|    | 1.4  | Backward compatibility                |    |

|    | 1.5  | Conventions used                      |    |

|    | 1.5  | 1.5.1 Visual cues (meta-syntax)       |    |

|    |      | 1.5.2 Notational conventions          |    |

|    |      | 1.5.3 Examples                        |    |

|    | 1.6  | Use of color in this standard         |    |

|    | 1.0  | Contents of this standard             |    |

| •  | D (  |                                       |    |

| 2. | Refe | rences                                | 5  |

| 3. | Defi | itions, acronyms, and abbreviations   | 7  |

|    | 3.1  | Definitions                           | 7  |

|    | 3.2  | Acronyms and abbreviations            | 8  |

| 4. | Lexi | cal conventions                       | 9  |

|    | 4.1  | White space                           |    |

|    | 4.2  | Comments                              |    |

|    | 4.3  | Identifiers                           | -  |

|    | 4.4  | Keywords                              |    |

|    | 4.5  | Strings                               |    |

|    | 4.6  | Numbers                               |    |

| 5. | Gen  | ral concepts, rules, and properties   | 13 |

|    | 5.1  | Key concepts and general rules        |    |

|    |      | 5.1.1 Defining components             |    |

|    |      | 5.1.2 Instantiating components        |    |

|    |      | 5.1.3 Specifying component properties |    |

|    |      | 5.1.4 Scoping and namespaces          |    |

|    | 5.2  | General component properties          |    |

|    |      | 5.2.1 Universal properties            |    |

|    |      | 5.2.2 Structural properties           |    |

|    | 5.3  | Content deprecation                   |    |

|    |      | 5.3.1 Semantics                       |    |

|    |      | 5.3.2 Examples                        |    |

| 6. | Data | types                                 | 29 |

|    | 6.1  | Overview                              | 29 |

|    | 6.2  | Primary data types                    |    |

|    |      | 6.2.1 Signed and unsigned data types  |    |

|    |      | 6.2.2 String data type                |    |

|    |      | 6.2.3 Boolean data type               |    |

|    |      | 6.2.4 Reserved enumeration types      |    |

|    |         | 6.2.5                                          | Enumerations                                                                                          |                                  |

|----|---------|------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------|

|    |         | 6.2.6                                          | Identifier references                                                                                 | 32                               |

|    | 6.3     | Aggreg                                         | ate data types                                                                                        | 33                               |

|    |         | 6.3.1                                          | Arrays                                                                                                | 33                               |

|    |         | 6.3.2                                          | Structures                                                                                            | 35                               |

|    | 6.4     | Type co                                        | ompatibility                                                                                          | 37                               |

|    | 6.5     | • •                                            | 1 · · · · · · · · · · · · · · · · · · ·                                                               |                                  |

|    |         |                                                |                                                                                                       |                                  |

| 7. | Expr    | essions                                        |                                                                                                       | 39                               |

|    | 7.1     |                                                | ew                                                                                                    |                                  |

|    | 7.2     | Operato                                        | ors                                                                                                   | 39                               |

|    |         | 7.2.1                                          | Assignment operators                                                                                  | 40                               |

|    |         | 7.2.2                                          | Logical operators                                                                                     |                                  |

|    | 7.3     | Express                                        | sion evaluation rules                                                                                 | 40                               |

|    |         | 7.3.1                                          | Rules for determining expression types                                                                | 40                               |

|    |         | 7.3.2                                          | Rules for evaluating expressions                                                                      | 41                               |

| 8. | Sign    | -1c                                            |                                                                                                       | 13                               |

| 0. | Signa   | ais                                            |                                                                                                       | 43                               |

|    | 8.1     |                                                | ction                                                                                                 |                                  |

|    | 8.2     | Signal p                                       | properties                                                                                            | 43                               |

|    |         | 8.2.1                                          | Semantics                                                                                             | 43                               |

|    |         | 8.2.2                                          | Example                                                                                               | 43                               |

|    | 8.3     | Signal o                                       | definition and instantiation                                                                          | 44                               |

|    |         | 8.3.1                                          | Semantics                                                                                             | 44                               |

|    |         | 8.3.2                                          | Example                                                                                               | 44                               |

| 9. | Field   | compon                                         | nent                                                                                                  | 45                               |

|    | 9.1     | Introdu                                        | iction                                                                                                | 45                               |

|    | 9.2     | Definin                                        | ng and instantiating fields                                                                           | 45                               |

|    | 9.3     |                                                | field instances                                                                                       |                                  |

|    | 9.4     | 0                                              | ccess properties                                                                                      |                                  |

|    | <i></i> | 9.4.1                                          | Semantics                                                                                             |                                  |

|    |         | 9.4.2                                          | Example                                                                                               |                                  |

|    | 9.5     |                                                | are signal properties                                                                                 |                                  |

|    |         |                                                | Semantics                                                                                             |                                  |

|    |         | 9.5.2                                          | Example                                                                                               |                                  |

|    | 9.6     |                                                | re access properties                                                                                  |                                  |

|    | 9.0     | 9.6.1                                          | Semantics                                                                                             |                                  |

|    |         | 9.6.2                                          | Examples                                                                                              |                                  |

|    | 9.7     |                                                | are access properties                                                                                 |                                  |

|    | 9.1     | 9.7.1                                          | Semantics                                                                                             |                                  |

|    |         | 9.7.1<br>9.7.2                                 |                                                                                                       |                                  |

|    | 0.0     |                                                | Example                                                                                               |                                  |

|    | 9.8     |                                                | r properties                                                                                          |                                  |

|    |         |                                                | Lounder incrementing and decrementing                                                                 |                                  |

|    |         | 9.8.1                                          | Counter incrementing and decrementing                                                                 |                                  |

|    | 0.5     | 9.8.2                                          | Counter saturation and threshold                                                                      | 54                               |

|    | 9.9     | 9.8.2<br>Interrup                              | Counter saturation and threshold<br>pt properties                                                     | 54<br>57                         |

|    | 9.9     | 9.8.2<br>Interrup<br>9.9.1                     | Counter saturation and threshold<br>pt properties<br>Semantics                                        | 54<br>57<br>61                   |

|    |         | 9.8.2<br>Interrup<br>9.9.1<br>9.9.2            | Counter saturation and threshold<br>pt properties<br>Semantics<br>Example                             | 54<br>57<br>61<br>61             |

|    |         | 9.8.2<br>Interrup<br>9.9.1<br>9.9.2<br>Miscell | Counter saturation and threshold<br>pt properties<br>Semantics<br>Example<br>laneous field properties | 54<br>57<br>61<br>61<br>61       |

|    |         | 9.8.2<br>Interrup<br>9.9.1<br>9.9.2            | Counter saturation and threshold<br>pt properties<br>Semantics<br>Example                             | 54<br>57<br>61<br>61<br>61<br>62 |

| 10. | Regi  | ster component                                                      | 63 |

|-----|-------|---------------------------------------------------------------------|----|

|     | 10.1  | Defining and instantiating registers                                | 63 |

|     |       | Instantiating registers                                             |    |

|     |       | Instantiating internal registers                                    |    |

|     |       | Instantiating external registers                                    |    |

|     |       | Instantiating alias registers                                       |    |

|     |       | 10.5.1 Semantics                                                    |    |

|     |       | 10.5.2 Example                                                      |    |

|     | 10.6  | Register properties                                                 |    |

|     | 10.0  | 10.6.1 Semantics                                                    |    |

|     |       | 10.6.2 Example                                                      |    |

|     | 10.7  | Understanding field ordering in registers                           |    |

|     | 10.7  | 10.7.1 Semantics                                                    |    |

|     |       | 10.7.2 Examples                                                     |    |

|     | 10.8  | Understanding interrupt registers                                   |    |

|     | 10.8  | 10.8.1 Semantics                                                    |    |

|     |       |                                                                     |    |

|     |       | 10.8.2 Example                                                      | 08 |

| 11. | Mam   | ory component                                                       | 60 |

| 11. | Men   | ory component                                                       | 09 |

|     | 11 1  | Defining and instantiating memories                                 | 60 |

|     |       | Semantics                                                           |    |

|     |       |                                                                     |    |

|     | 11.5  | Memory properties                                                   |    |

|     |       |                                                                     |    |

|     |       | 11.3.2 Example                                                      | /0 |

| 12. | Regi  | ster file component                                                 | 71 |

|     | C     |                                                                     |    |

|     | 12.1  | Defining and instantiating register files                           | 71 |

|     |       | Semantics                                                           |    |

|     | 12.3  | Register file properties                                            | 72 |

|     |       | 12.3.1 Semantics                                                    |    |

|     |       | 12.3.2 Example                                                      |    |

|     |       | 1                                                                   |    |

| 13. | Addı  | ess map component                                                   | 75 |

|     |       |                                                                     |    |

|     |       | Introduction                                                        |    |

|     |       | Defining and instantiating address maps                             |    |

|     |       | Semantics                                                           |    |

|     | 13.4  | Address map properties                                              | 75 |

|     |       | 13.4.1 Semantics                                                    | 76 |

|     |       | 13.4.2 Example                                                      | 77 |

|     | 13.5  | Defining bridges or multiple view address maps                      | 77 |

|     |       | 13.5.1 Semantics                                                    | 77 |

|     |       | 13.5.2 Example                                                      | 77 |

|     |       |                                                                     |    |

| 14. | Verit | ication constructs                                                  | 79 |

|     | 1/1   | HDI nath                                                            | 70 |

|     | 14.1  | HDL path                                                            |    |

|     |       | <ul><li>14.1.1 Assigning HDL path</li><li>14.1.2 Examples</li></ul> |    |

|     | 140   | Constraints                                                         |    |

|     | 14.2  |                                                                     |    |

|     |       | 14.2.1 Describing constraints                                       | 01 |

|       |       | 14.2.2<br>14.2.3 | Constraint component<br>Example                    |      |

|-------|-------|------------------|----------------------------------------------------|------|

|       |       | _                |                                                    |      |

| 15.   | User- | defined p        | properties                                         | . 85 |

|       | 15.1  | Defining         | g user-defined properties                          | . 85 |

|       |       | 15.1.1           | Semantics                                          | . 86 |

|       |       | 15.1.2           | Example                                            | . 86 |

|       | 15.2  | Assignir         | ng (and binding) user-defined properties           | . 86 |

|       |       | 15.2.1           | Semantics                                          | . 86 |

|       |       | 15.2.2           | Examples                                           | . 87 |

| 16.   | Prepr | ocessor d        | lirectives                                         | . 89 |

|       | 16.1  | Embedd           | ed Perl preprocessing                              | . 89 |

|       |       | 16.1.1           | Semantics                                          | . 89 |

|       |       | 16.1.2           | Example                                            | . 89 |

|       | 16.2  | Verilog-         | style preprocessor                                 | . 89 |

|       |       | 16.2.1           | Verilog-style preprocessor directives              | . 90 |

|       |       | 16.2.2           | Limitations on nested file inclusion               | . 90 |

| 17.   | Adva  | nced topi        | cs in SystemRDL                                    | . 91 |

|       | 17.1  | Applicat         | ion of signals for reset                           | . 91 |

|       |       |                  | anding hierarchical interrupts in SystemRDL        |      |

|       |       | 17.2.1           | Example structure and perspective                  |      |

|       |       | 17.2.2           | Code snippet 1                                     | . 95 |

|       |       | 17.2.3           | Code snippet 2                                     | . 95 |

|       |       | 17.2.4           | Code snippet 3                                     | . 96 |

|       |       | 17.2.5           | Code snippet 4                                     | . 96 |

|       |       | 17.2.6           | Code snippet 5                                     | . 97 |

|       |       | 17.2.7           | Code snippet 6                                     | . 98 |

|       |       | 17.2.8           | Code snippet 7                                     | . 98 |

|       |       | 17.2.9           | Code snippet 8                                     |      |

|       |       |                  | Code snippet 9                                     |      |

|       |       |                  | Code snippet 10                                    |      |

|       |       |                  | Code snippet 11                                    |      |

|       | 17.3  |                  | anding bit ordering and byte ordering in SystemRDL |      |

|       |       | 17.3.1           | Bit ordering                                       |      |

|       |       | 17.3.2           | Byte ordering                                      | 104  |

| Annex | А     | (informa         | tive) Bibliography                                 | 105  |

| Annex | В     | (normati         | ve) Grammar                                        | 107  |

| Annex | С     | (informa         | tive) Backward compatibility                       | 113  |

| Annex | D     | (normati         | ve) Reserved words                                 | 117  |

| Annex | Е     | (normati         | ve) Access modes                                   | 119  |

| Annex | F     | (informa         | tive) Formatting text strings                      | 127  |

| Annex | G     | (informa         | tive) Component-property relationships             | 131  |

# SystemRDL 2.0: A Register Description Language Specification

# 1. Overview

This clause explains the scope and purpose of this standard, describes the key features, details the conventions used, and summarizes its contents.

The formal syntax of SystemRDL is described using Backus-Naur Form (BNF), which is summarized in <u>Annex B</u>. The rest of this Standard is intended to be consistent with the SystemRDL grammar. If any discrepancies between the two occur, the grammar in <u>Annex B</u> shall take precedence.

# 1.1 Scope

SystemRDL is a language for the design and delivery of intellectual property (IP) products used in designs. SystemRDL semantics supports the entire life-cycle of registers from specification, model generation, and design verification to maintenance and documentation. Registers are not just limited to traditional configuration registers, but can also refer to register arrays and memories.

The intent of this standard is to define SystemRDL accurately. Its primary audience are implementers of tools supporting the language and users of the language. The focus is on defining the valid language constructs, their meanings and implications for the hardware and software that is specified or configured, how compliant tools are required to behave, and how to use the language.

# 1.2 Purpose

SystemRDL is designed to increase productivity, quality, and reuse during the design and development of complex digital systems. It can be used to share IP within and between groups, companies, and consortiums. This is accomplished by specifying a single source for the register description from which all views can be automatically generated, which ensures consistency between multiple views. A *view* is any output generated from the SystemRDL description, e.g., RTL code or documentation.

# 1.3 Motivation

SystemRDL was created to minimize problems encountered in describing and managing registers. Typically in a traditional environment the system architect or hardware designer creates a functional specification of the registers in a design. This functional specification is most often text and lacks any formal syntactic or

semantic rules. This specification is then used by other members of the team including software, hardware, and design verification. Each of these parties uses the specification to create representations of the data in the languages which they use in their aspect of the chip development process. These languages typically include Verilog, VHDL, C, C++, Vera, e, and SystemVerilog. Once the engineering team has an implementation in a HDL and some structures for design verification, then design verification and software development can begin.

During these verification and validation processes, bugs are often encountered which require the original register specification to change. When these changes occur, all the downstream views of this data have to be updated accordingly. This process is typically repeated numerous times during chip development. In addition to the normal debug cycle, there are two additional aspects that can cause changes to the register specification. First, marketing requirements can change, which require changes to a register's specification. Second, physical aspects, such as area and timing constraints can drive changes to the register's specification. There are clearly a number of challenges with this approach:

- a) The same information is being replicated in many locations by many individuals.

- b) Propagating the changes to downstream customers is tedious, time-consuming, and error-prone.

- c) Documentation updates are often postponed until late in the development cycle due to pressures to complete other more critical engineering items at hand.

These challenges often result in a low-quality product and wasted time due to having incompatible register views. SystemRDL was designed to eliminate these problems by defining a rich language that can formally describe register specifications. Through application of SystemRDL and a SystemRDL compiler, users can save time and eliminate errors by using a single source of specification and automatically generating any needed downstream views.

# 1.4 Backward compatibility

One of the main goals for this update to the SystemRDL specification was to maintain backward compatibility to SystemRDL 1.0. In some cases, however, this was not possible. <u>Annex C</u> shows the known areas of incompatibility in advancing the SystemRDL specification from the SystemRDL1.0 to SystemRDL 2.0 versions.

# 1.5 Conventions used

The conventions used throughout the document are included here.

# 1.5.1 Visual cues (meta-syntax)

The meta-syntax for the description of the syntax rules uses the conventions shown in Table 1.

| Visual cue | Represents                                                                                                                                                                                                                                                                                                    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bold       | The <b>bold</b> font is used to indicate key terms, text that shall be typed exactly as it appears.<br>For example, in the following property definition, the keyword "default" and special char-<br>acter ":" (and optionally "=") shall be typed as they appear:<br><b>default</b> property_name [= value]; |

| italic     | The <i>italic</i> font in running text represents user-defined variables. For example, a property name needs to be specified in the following line (after the "default" key term):<br><b>default</b> property_name [= value];                                                                                 |

# Table 1—Document conventions

| Visual cue                                                                                                                                                                                                                                  | Represents                                                                                                                                                                                                               |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| courier                                                                                                                                                                                                                                     | The courier font in running text indicates SystemRDL or HDL code. For example, the following line indicates SystemRDL code:                                                                                              |  |

|                                                                                                                                                                                                                                             | field myField {}; // defines a field type named "myField"                                                                                                                                                                |  |

| plain text                                                                                                                                                                                                                                  | The <u>normal</u> or <u>plain text</u> font in the BNF indicates syntactic categories (see <u>Annex B</u> ).                                                                                                             |  |

| [] square brackets                                                                                                                                                                                                                          | Square brackets indicate optional parameters. For example, the value assignment is optional in the following line:<br>default property_name [= value];                                                                   |  |

| <pre>{ } curly braces Curly braces ({ }) indicate items that can be repeated zero or more times. For the following shows one or more universal properties can be specified for this mnemonic_name = value [{{universal_property;}*}];</pre> |                                                                                                                                                                                                                          |  |

| * asterisk                                                                                                                                                                                                                                  | An asterisk (*) signifies that parameter can be repeated. For example, the following line means multiple properties can be specified for this command:<br><b>field</b> {[property;]*} name = value;                      |  |

| separator bar                                                                                                                                                                                                                               | The separator bar ( ) character indicates alternative choices. For example, the following line shows the "in" or "out" key terms are possible values for the "-direction" parameter:<br>-direction <in out=""  =""></in> |  |

# Table 1—Document conventions (Continued)

# **1.5.2 Notational conventions**

The terms "required", "shall", "shall not", "should", "should not", "recommended", "may", and "optional" in this document are to be interpreted as described in the IETF Best Practices Document 14, RFC 2119.<sup>1</sup>

# 1.5.3 Examples

Any examples shown in this Standard are for information only and are only intended to illustrate the use of SystemRDL.

# 1.6 Use of color in this standard

This standard uses a minimal amount of color to enhance readability. The coloring is not essential and does not affect the accuracy of this standard when viewed in pure black and white. The places where color is used are the following:

- Cross references that are hyperlinked to other portions of this standard are shown in <u>underlined-blue</u> <u>text</u> (hyperlinking works when this standard is viewed interactively as a PDF file).

- Syntactic keywords and tokens in the formal language definitions are shown in **boldface-red text** when initially defined.

# 1.7 Contents of this standard

The organization of the remainder of this standard is as follows:

<sup>&</sup>lt;sup>1</sup>Information on references can be found in <u>Clause 2</u>.

- <u>Clause 2</u> provides references to other applicable standards that are assumed or required for this standard.

- <u>Clause 3</u> defines terms and acronyms used throughout the different specifications contained in this standard.

- <u>Clause 4</u> defines the lexical conventions used in SystemRDL.

- <u>Clause 5</u> highlights the general concepts, rules, and properties in SystemRDL.

- <u>Clause 6</u> defines the SystemRDL data types.

- <u>Clause 7</u> describes how expressions are used in SystemRDL.

- <u>Clause 8</u> describes how signals are used in SystemRDL.

- <u>Clause 9</u> defines the field components.

- <u>Clause 10</u> defines the register components.

- <u>Clause 11</u> defines the memory components.

- <u>Clause 12</u> defines the register file components.

- <u>Clause 13</u> defines the address map components.

- <u>Clause 14</u> specifies the verification constructs.

- <u>Clause 15</u> specifies the user-defined properties.

- <u>Clause 16</u> defines the preprocessor directives.

- <u>Clause 17</u> describes advanced uses of SystemRDL.

- Annexes. Following <u>Clause 17</u> are a series of annexes.

# 2. References

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments or corrigenda) applies.

IEEE Std 1364<sup>™</sup>, IEEE Standard for Verilog Hardware Description Language.<sup>2, 3</sup>

IEEE Std 1685<sup>™</sup>, IEEE Standard for IP-XACT, Standard Structure for Packaging, Integrating, and Reusing IP within Tool Flows.

IEEE Std 1800<sup>™</sup>, IEEE Standard for SystemVerilog Unified Hardware Design, Specification and Verification Language.

IEEE Std 1800.2<sup>™</sup>, IEEE Standard for Universal Verification Methodology Language Reference Manual.

IETF Best Practices Document 14, RFC 2119.

The Apache ASP Embedding Syntax is available from the Apache web site: <u>http://www.apache-asp.org/syntax.html</u>.

The HTML 4.01 standard syntax is available from the W3 web site: <u>http://www.w3.org/TR/html401/</u>.

The MD5 Message-Digest Algorithm is available from the IETF web site: <u>https://tools.ietf.org/html/rfc1321</u>.

The Perl programming language, Version 5, is available from the Perl web site: <u>http://www.perl.org/</u>.

The Unicode Standard, Version 9.0.0, is available from The Unicode Consortium web site: <u>http://www.unicode.org/versions/Unicode9.0.0/</u>.

<sup>&</sup>lt;sup>2</sup>The IEEE standards or products referred to in this clause are trademarks of the Institute of Electrical and Electronics Engineers, Inc. <sup>3</sup>IEEE publications are available from the Institute of Electrical and Electronics Engineers, Inc., 445 Hoes Lane, Piscataway, NJ 08854, USA (http://standards.ieee.org/).

# 3. Definitions, acronyms, and abbreviations

For the purposes of this document, the following terms and definitions apply. *The Authoritative Dictionary of IEEE Standards Terms* [B1]<sup>4</sup> should be referenced for terms not defined in this clause.

# 3.1 Definitions

address map: Defines the organization of the registers, register files, memories, and address maps into a software addressable space. Address maps can be organized hierarchically.

**byte order**: The ordering of the bytes from left to right or right to left or from most significant byte to least significant byte or least significant byte to most significant byte. This is often referred to as *endianness*. See also <u>Clause 17</u>.

**bit order**: The ordering of the bits from left to right or right to left or from most significant bit to least significant bit to most significant bit. See also <u>Clause 17</u>.

**component**: A basic building block in SystemRDL that acts as a container for information. Similar to a *struct* or *class* in programming languages.

constraint: An assertion made for verification purposes that is evaluated at the runtime of the design.

element: An instantiation of any SystemRDL component type.

enumeration: Used in field encodings and component property encodings. An identifier bound to some bit value or a list of values describing bit field encoding or component property encoding.

field: The most basic component object. Fields serve as an abstraction of hardware storage elements.

**keyword**: A predefined, non-escaped identifier (see 4.3) that defines a language construct; keywords cannot be used as identifiers.

**memory**: A contiguous array of memory data elements. A data structure within a memory can be specified with virtual registers or register files.

**parameter**: A generalized value of a **component** definition that can be modified for each instance of the component.

**property**: A characteristic, attribute, or a trait of a **component** in SystemRDL. Because they exist in their own namespace, property names do not conflict with the language and are not restricted as identifiers.

**RDLFormatCode**: A set of formatting tags which can be used on text strings.

register: A set of one or more fields which are accessible by software at a particular address.

register file: A grouping of registers and other register files. Register files can be organized hierarchically.

**reserved words**: terms which have a similar effect to **keywords**; all reserved words are explicitly reserved for future use.

<sup>&</sup>lt;sup>4</sup>The number in brackets correspond to those of the bibliography in <u>Annex A</u>.

signal: A wire used for interconnect or to define additional component inputs and/or outputs.

struct: User-defined structure for use in user-defined properties. See also <u>Clause 15</u>.

# 3.2 Acronyms and abbreviations

- HDL hardware description language

- HTML hypertext markup language

- IP intellectual property

- LSB least significant bit

- MSB most significant bit

- RTL register transfer level

# 4. Lexical conventions

This clause describes SystemRDL in terms of lexical conventions. SystemRDL source code is comprised of a stream of lexical tokens consisting of one or more characters. SystemRDL files shall use the Universal Coded Character Set, UCS, encoded using UTF-8. UCS code points beyond the ASCII code page are restricted to comments and character strings. SystemRDL is case-sensitive. SystemRDL identifiers are limited to ASCII letters, numbers, and the underscore (\_). The support for UTF-8 is limited to strings to allow for non-English documentation. SystemRDL compilers shall ignore the byte-order mark.

# 4.1 White space

White space characters are: space (U+0020), horizontal tab (U+0009), line feed (U+000A), and carriage return (U+000D). All white space characters are syntactically insignificant, except in the following cases.

- a) Strings—Any number of consecutive white space characters is treated as a single space for purposes of generating documentation. See <u>4.5</u>.

- b) Single-line comments—A new-line character (*line feed, carriage return*, or *line feed* plus *carriage return*) terminates a single-line comment. See <u>4.2</u>.

- c) Where more than one token is being used and spacing is required to separate the tokens.

# 4.2 Comments

There are two types of comments in SystemRDL: single-line comments and block comments. *Single-line comments* begin with // and are terminated by a new-line character. *Block comments* begin with /\* and are terminated by the next \*/. Block comments may span any number of lines; they shall not be nested. Within a block comment, a single-line comment (//) has no significance.

Examples

# 4.3 Identifiers

An *identifier* assigns a name to a user-defined data type or its instance. There are two types of identifiers: simple and escaped. Identifiers are case-sensitive. *Simple identifiers* have a first character that is a letter or underscore (\_) followed by zero or more letters, digits, and underscores. *Escaped identifiers* begin with \ followed by a simple identifier.

Examples

```

my_identifier

My_IdEnTiFiEr

x

_Y0123

_3

\field // This is escaped because it uses a keyword

```

# 4.4 Keywords

*Keywords* are predefined, non-escaped identifiers (see 4.3) that define language constructs. Keywords cannot be used as identifiers. Escaped keywords are treated as identifiers in SystemRDL. The keywords are listed in Table 2.

| Table 2—SystemRDL keywords |                |                |           |           |  |

|----------------------------|----------------|----------------|-----------|-----------|--|

| abstract                   | accesstype     | addressingtype | addrmap   | alias     |  |

| all                        | bit            | boolean        | bothedge  | compact   |  |

| component                  | componentwidth | constraint     | default   | encode    |  |

| enum                       | external       | false          | field     | fullalign |  |

| hw                         | inside         | internal       | level     | longint   |  |

| mem                        | na             | negedge        | nonsticky | number    |  |

| onreadtype                 | onwritetype    | posedge        | property  | r         |  |

| rclr                       | ref            | reg            | regalign  | regfile   |  |

| rset                       | ruser          | rw             | rw1       | signal    |  |

| string                     | struct         | SW             | this      | true      |  |

| type                       | unsigned       | w              | w1        | wclr      |  |

| woclr                      | woset          | wot            | wr        | wset      |  |

| wuser                      | wzc            | WZS            | wzt       |           |  |

The following also apply.

- *Reserved words* have a similar effect as *keywords*; reserved words are explicitly reserved for future use. See also <u>Annex D</u>.

- The SystemRDL-detailed access modes are defined in <u>Annex E</u>.

- Right-hand side values defined in this standard are keywords. See also Annex G.

- Left-hand side values that are not keywords are properties. See also <u>Annex G</u>.

- Because they exist in their own namespace, *property names* do not conflict with the language and are not restricted as identifiers.

# 4.5 Strings

A *string* is a sequence of characters enclosed by double quotes. The escape sequence  $\backslash''$  can be used to include a double quote within a string. To maintain consistency between all generated documentation formats, one or more consecutive white space characters within a string shall be converted to a single space for purposes of documentation generation. SystemRDL also has a set of formatting tags which can be used on text strings, see <u>Annex F</u>.

Examples

```

"This is a string"

"This is also

a string!"

"This third string contains a \"double quote\""

```

# 4.6 Numbers

There are several number formats in SystemRDL. All numbers in SystemRDL are unsigned.

- a) Simple decimal: A sequence of decimal digits 0, ..., 9.

- b) Simple hexadecimal: 0x (or 0X) followed by a sequence of decimal digits or characters a through f (upper- or lower-case).

- c) Verilog-style decimal: Begins with a *width* specifying the number of binary bits (a positive decimal number) followed by a single quote ('), followed by a d or D for decimal, and then the number itself, represented as a sequence of digits 0 through 9.

- d) Verilog-style hexadecimal: Begins with a *width* specifying the number of binary bits (a positive decimal number) followed by a single quote ('), followed by an h or H for hexadecimal), and then the number itself, represented as a sequence of digits 0 through 9 or characters a through f (upper- or lower-case).

- e) Verilog-style binary: Begins with a *width* specifying the number of binary bits (a positive decimal number) followed by a single quote ('), followed by a **b** or **B** for binary, and then the number itself, represented as a sequence of the digits 0 and 1.

The numeric portion of any number may contain multiple underscores (\_) at any position, except the *width* and first position, which are ignored in the computation of the associated numeric value. Additionally the *width* of a Verilog number needs to be specified. Ambiguous *width* Verilog-style numbers, e.g., 'hFF, are not supported.

It shall be an error if the value of a Verilog-style number does not fit within the specified bit-width.

Examples

# 5. General concepts, rules, and properties

The concepts, rules, and properties described in this clause are common to all component types and do not determine how a component is implemented in a design.

# 5.1 Key concepts and general rules

This subclause describes the key concepts of SystemRDL and documents general rules about how to use the language to define hardware specifications. Subsequent clauses will refine these generic rules for each component type.

A *component* in SystemRDL is the basic building block or a container which contains properties that further describe the component's behavior. There are several structural components in SystemRDL: field, reg, mem, regfile, and addrmap. Additionally, there are several non-structural components: signal, enum, and constraint.

Components can be defined in any order, as long as each component is defined before it is instantiated. All structural components (and signals) need to be instantiated before being generated.

# 5.1.1 Defining components

To define components in SystemRDL, each *definition statement* shall begin with the keyword corresponding to the component object being defined (as listed in <u>Table 3</u>). All components need to be defined before they can be instantiated (see 5.1.2).

| Туре          | Keyword    |

|---------------|------------|

| Field         | field      |

| Register      | reg        |

| Register file | regfile    |

| Address map   | addrmap    |

| Signal        | signal     |

| Enumeration   | enum       |

| Memory        | mem        |

| Constraint    | constraint |

Table 3—Component types

SystemRDL components can be defined in two ways: definitively or anonymously.

- *Definitive* defines a named component type, which is instantiated in a separate statement. The definitive definition is suitable for reuse.

- Anonymous defines an unnamed component type, which is instantiated in the same statement (see also <u>5.1.2</u>). The anonymous definition is suitable for components that are used once.

A *definitive definition* of a component appears as follows.

component new\_component\_name [#(parameter\_definition [, parameter\_definition]\*)]

{[component\_body]} [instance\_element [, instance\_element]\*];

An anonymous definition (and instantiation) of a component appears as follows.

component {[component\_body]} instance\_element [, instance\_element]\*;

- a) In both cases, *component* is one of the keywords specified in <u>Table 3</u>.

- b) For a definitively defined component, *new\_component\_name* is the user-specified name for the component.

- c) For a definitively defined component, *parameter\_definition* is the user-specified parameter as defined in <u>5.1.1.1</u>.

- d) For a anonymously defined component, *instance\_element* is the description of the instantiation attributes, as defined in 5.1.2 a 3.

- e) The *component\_body* is comprised of zero or more of the following.

- 1) Default property assignments

- 2) Property assignments

- 3) Component instantiations

- 4) Nested component definitions

- 5) Constraint definitions

- 6) Struct definitions

- f) The first instance name of an anonymous definition is also used as the component type name.

- g) The stride (+=), alignment (%), and offset (@) of anonymous instances are the same as the definitive instances in 5.1.2.3.

The following code fragment shows a simple definitive field component definition for myField.

field myField {};

The following code fragment shows a simple anonymous field component definition for myField.

field {} myField;

# 5.1.1.1 Defining component parameters

All definitive component types, except enumerations and constraints, may be parametrized using Verilogstyle parameters. To define Verilog-style parameters in SystemRDL, parameter definitions shall be specified after the component's name. *parameter\_definition* is defined as follows.

parameter\_type parameter\_name [= parameter\_value]

where

- a) *parameter type* is a type reference taken from the list of SystemRDL types (see <u>Table 7</u>).

- b) *parameter\_name* is a user-specified parameter name.

- c) *parameter value* is an expression whose resolved type should be consistent with *parameter type*.

#### 5.1.1.2 Semantics

- a) If a parameter definition is assigned a parameter value, that value is the default value for the parameter.

- b) If a parameter is not specified with a default value, every instance of the component needs to provide a value for the parameter.

- c) The name of the parameter may be used elsewhere within the remainder of the component definition to represent its value.

- d) Nested component definitions do not inherit from their parent's parameters.

- e) Component instance references shall not be used as parameter values (either directly or as part of an aggregate type).

# 5.1.1.3 Inserting parameterized types in the type namespace

Each declared component's type name is added to the type namespace of the enclosing scope of component declaration. In addition, instances of parameterized components which have parameter overrides create a new type name based on the parameterized component type name rules in the type namespace of the component declaration enclosing scope. Subsequent instances of parameterized components with the same resolved parameter values matching those of a component instance existing type name in the type namespace of component declaration enclosing shall reuse the existing type name without adding a new type name.

It shall be an error if a parameterized component instance has a type name which matches an existing type name that corresponds to a parameterized component instance with different resolved parameter values or matches any other type name.

# 5.1.1.4 Generated type naming rules

Most generation targets for elaborated SystemRDL platforms require some means of uniquely identifying instance types. To provide a minimum level of compatibility between tool outputs, defining the type name generation process is necessary.

The following steps shall be used to construct the elaborated type names of instance with parameter arguments.

- a) If the instance's defined arguments match the type's default parameter values, the instance's type name shall be used as is.

- b) If the instance's type is parameterized and all the defined arguments match the type's default parameter values, the instance's type name shall be used as is.

- c) In all other cases, the instance's generated type name shall be constructed by appending to the instance's type name and, for each argument its name, followed by its normalized value, separated by a single underscore (). The sequences shall also be joined using single underscores.

type\_name {(\_param\_name\_normalized\_value)}\*

Normalized values shall be derived from the argument's type and from its resolved expression's value as follows.

- 1) Scalar values shall be rendered using their hexadecimal representation.

- 2) Boolean values shall be rendered using either t for **true** or f for **false**.

- 3) String values shall be rendered using the first eight characters of their md5 (*Message-Digest Algorithm*) checksum.

- 4) Enum values shall be rendered using their enumerator literal.

- 5) Arrays shall be rendered by:

- i) generating the normalized values of its elements,

- ii) joining these elements with single underscores (\_) into a single character sequence, and

- iii) using the first eight characters of the md5 checksum of this character sequence

... which can be semi-formalized as:

subsequence( md5( join( normalized\_values, '\_'), 0, 8 )

6) Structs shall be rendered by:

- i) generating the normalized value of each member,

- ii) joining each member's name with its normalized value, separated by a single underscore (\_),

- iii) joining the member character sequences with single underscores,

- iv) using the first eight characters of the md5 checksum of this character sequence ... which can be semi-formalized as:

member\_normalization = concat( member\_name, '\_', normalized\_member\_value )

subsequence( md5( join( apply( struct\_members, member\_normalization ) ), 0, 8)

# 5.1.2 Instantiating components

In a similar fashion to defining components, SystemRDL components can be instantiated in two ways.

a) A definitively defined component is instantiated in a separate statement, as follows. type name [#(parameter instance [, parameter instance]\*)]

instance\_element [, instance\_element]\*;

where

- 1) *type\_name* is the user-specified name for the component.

- 2) *parameter\_instance* is specified as

```

.param_name(param_val)

```

where *param\_name* is the name of the parameter defined with the component and *param\_val* is an expression whose result is the value of the parameter for this instance.

- 3) instance\_element is specified as follows. instance\_name [{[constant\_expression]}\* | [constant\_expression : constant\_expression]] [addr\_alloc]

- i) *instance\_name* is the user-specified name for instantiation of the component.

- ii) constant\_expression is an expression that resolves to a longint unsigned.

- iii) [*constant\_expression*] specifies the size of the instantiated component array (optionally multidimensional) if the component is an **addrmap**, a **regfile**, a **reg**, or a **mem**; or the instantiated component's bit width if the component is a **field** or a **signal**.

- iv) [constant\_expression : constant\_expression] specifies the bit boundaries of the instantiated component. This form of instantiation can only be used for **field** or **signal** components (see <u>Clause 10</u> and <u>Clause 8</u>).

- v) *addr\_alloc* is an address allocation operator (see <u>5.1.2.3</u>). These operators shall only be used when instantiating **addrmap**, **regfile**, **reg**, or **mem** components.

- vi) When using multiple-dimensions, the last subscript increments the fastest.

- b) An *anonymously defined component* is instantiated in the statement that defines it (see also <u>5.1.1</u>).

Components need to be defined before they can be instantiated. In some cases, the order of instantiation impacts the structural implementation, e.g., for the assigning of bit positions of fields in registers (see Clause 6 — Clause 15).

The following code fragment shows a simple scalar field component instantiation.

field {} myField; // single bit field instance named "myField"

The following code fragment shows a simple array field component instantiation.

field {} myField[8]; // 8 bit field instance named "myField"

# 5.1.2.1 Specifying instance parameters

SystemRDL components defined with parameters (see 5.1.1.1) may have those parameters overridden or defined during non-anonymous instantiation.

Parameters are assigned by name, which explicitly links the parameter name and its new value. The name of the parameter shall be the name specified in the instantiated component. It is not necessary to assign values to all of the parameters within a component, only parameters that are assigned new values need to be specified. Parameter values are assigned using Verilog-style syntax, as defined in <u>5.1.2 a 2</u>.

# 5.1.2.1.1 Parameter instance example

```

reg myReg #(longint unsigned SIZE = 32, boolean SHARED = true) {

regwidth = SIZE;

shared = SHARED;

field {} data[SIZE - 1];

};

addrmap myAmap {

myReg reg32;

myReg reg32_arr[8];

myReg #(.SIZE(16)) reg16;

myReg #(.SIZE(8), .SHARED(false)) reg8;

};

```

# 5.1.2.1.2 Parameter dependence

- a) A parameter (e.g., memory\_size) can be defined with an expression containing another parameter (e.g., word size).

- b) Overriding a parameter effectively replaces the parameter definition with the new expression.

- c) Parameters are evaluated following the order in which they are defined in the component definition. Because memory\_size depends on the value of word\_size, a modification of word\_size changes the value of memory\_size.

For example, in the following parameter declaration, an update of word\_size in an instantiation statement for the component that defined these parameters automatically updates memory\_size. If memory\_size is defined in an instantiation statement, however, it will take on that value, regardless of the value of word\_size.

# 5.1.2.2 Instance address allocation

The offset of an instance within an object is always relative to its parent object. If an instance is not explicitly assigned an address allocation operator (see <u>Table 4</u>), the compiler assigns the address according to the **alignment** (see <u>5.1.2.2.1</u>) and *addressing mode* (see <u>5.1.2.2.2</u>). The address of an instance from the top level addrmap is calculated by adding the instance offset and the offset of all its parent objects.

# 5.1.2.2.1 Instance alignment

The **alignment** property defines the byte value of which the container's instance addresses shall be a multiple. This property can be set for **addrmaps** (see <u>Table 26</u>) and **regfiles** (see <u>Table 25</u>), and its value

shall be a power of two (1, 2, 4, etc.). Its value is inherited by all of the container's non-addrmap children. By default, instantiated objects shall be aligned to a multiple of their width (e.g., the address of a 64-bit register is aligned to the next 8-byte boundary).

#### 5.1.2.2.2 Addressing modes

There are three *addressing modes* defined in SystemRDL: **compact**, **regalign** (the default), and **fullalign**. These addressing modes are set using the **addressing** address map property (see <u>Table 26</u>).

a) compact

Specifies the components are packed tightly together while still being aligned to the **accesswidth** parameter (see <u>Table 23</u>).

Example 1

```

Sets accesswidth=32.

```

Example 2

Sets accesswidth=64.

};

## b) regalign

Specifies the components are packed so each component's start address is a multiple of its size (in bytes). Array elements are aligned according to the individual element's size (this results in no gaps between the array elements). This generally results in simpler address decode logic.

#### Example 3

Uses the default accesswidth of 32.

```

addrmap some_map {

addressing = regalign;

reg { field {} a; } a;  // Address 0

reg { regwidth=64; field {} a; } b; // Address 8

```

```

reg { field {} a; } c[20]; // Address 0x10

// Address 0x14 - Element 1

// Address 0x18 - Element 2

```

# };

#### c) fullalign

The assigning of addresses is similar **regalign**, except for arrays. The alignment value for the first element in an array is the size in bytes of the whole array (i.e., the size of an array element multiplied by the number of elements), rounded up to nearest power of two. The second and subsequent elements are aligned according to their individual size (so there are no gaps between the array elements).

#### Example 4

Uses the default accesswidth of 32.

#### 5.1.2.3 Address allocation operators

When instantiating **regs**, **regfiles**, **mems**, or **addrmaps**, the address may be assigned using one of the address allocation (addr alloc) operators in <u>Table 4</u>.

| Property            | Implementation/Application                                                                                                                                                                                                                                      |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <i>a</i> expression | Specifies the address for the component instance. This expression resolves to a longint unsigned.                                                                                                                                                               |  |  |

| += expression       | Specifies the address stride when instantiating an array of components (controls the spacing of the components). The address stride is relative to the previous instance's address. This expression resolves to a longint unsigned.                             |  |  |

| %= expression       | Specifies the alignment of the next address when instantiating a component (con-<br>trols the alignment of the components). The initial address alignment is relative to<br>the previous instance's address. This expression resolves to a longint<br>unsigned. |  |  |

# Table 4—Address allocation operators

#### 5.1.2.4 Semantics

- a) Addresses in SystemRDL are always byte addresses.

- b) Addresses are assigned in incrementing order.

- c) The operator %= is a more localized version of the **alignment** property (see <u>Table 25</u>).

- d) The expression used for address specification shall be resolvable to a longint unsigned.

- e) The += operator is only used when instantiating arrayed **addrmap**, **regfile**, **reg**, or **mem** components.

- f) The (a) and %= operators are mutually exclusive per instance.

- g) The alignment of an array instance specifies the alignment of the start of the array and the increment specifies the offset from one array element to the next array element.

#### 5.1.2.5 Examples

The following set of examples demonstrate the usage of the operators defined in <u>Table 4</u>. The final addresses (as indicated in the comments in the example) are valid for an addressing mode called **regalign**, which is the default addressing mode (see <u>Clause 13</u>), with the default **regwidth=**32. The **regfile** component is defined in <u>Clause 12</u>.

#### Example 1

Using the @ operator.

Example 2

Using the += operator.

#### Example 3

Using the %= operator.

```

};

};

```

#### 5.1.3 Specifying component properties

Each property is associated with at least one data type defined in <u>Clause 6</u> (and summarized in <u>Table 7</u>). Property types include primitive types and aggregate types.

#### 5.1.3.1 Property assignment

Each component type has its own set of pre-defined properties. Properties may be assigned in any order. User-defined properties can also be specified to add additional properties to a component that are not pre-defined by the SystemRDL specification (see <u>Clause 15</u>). A specific property shall only be set once per scope (see <u>5.1.4</u>). All component property assignments are optional.

A property assignment appears as follows.

property\_name [= expression];

The descriptions for the data types of *expression* results that are legal for each *property\_name* (and exceptions to those rules) are explained in the corresponding clause for each individual component (see <u>Clause 8</u> — <u>Clause 14</u>).

When *expression* is not specified, it is presumed the *property\_name* is of type **boolean** and the default value is set to **true**.

Example

#### 5.1.3.2 Assigning default values

Default values for a given property can be set within the current or any enclosing lexical scope (see 5.1.4). Any components defined in the same or enclosed lexical scope as the default property assignment shall use the default values for properties in the component not explicitly assigned in a component definition. A specific property **default** value shall only be set once per scope.

A default property assignment appears as follows.

default property\_name [= value];

The descriptions for the types of *values* that are legal for each *property\_name* (and exceptions to those rules) are explained in the corresponding clause for each individual component (see <u>Clause 8</u> — <u>Clause 14</u>).

When the *value* is not specified, the property shall be assigned the boolean value **true**.

Example

```

field {} outer_field ;

reg {

default name = "default name";

```

#### 5.1.3.3 Dynamic assignment

Some properties may have their values assigned or overridden on a per-instance basis. When a property is assigned after the component is instantiated, the assignment itself is referred to as a *dynamic assignment*. Properties of a referenced instance shall be accessed via the arrow operator (->).

A dynamic assignment appears as follows.

instance name -> property name [= value];

where

- a) *instance\_name* is a previously instantiated component (see <u>5.1.2</u>).

- b) When *value* is not specified, it is presumed the *property\_name* is of type **boolean** and the value is set to **true**.

- c) The dynamically assignable properties for each component type are explained in the corresponding clause for each individual component (see <u>Clause 8</u> <u>Clause 14</u>).

- d) In the case where *instance\_name* is an array, the following possible dynamic assignment scenarios exist.

- 1) If the component type is **field** or **signal**, the fact the component is an array does not matter—the assignment is treated as if the component were a not an array.

- 2) If the component type is reg, regfile, mem, or addrmap

- The user can dynamically assign the property for all elements of the array by eliminating the square brackets ([]) and the array index from the dynamic assignment.

array instance name -> property name [= value];

- ii) The user can dynamically assign the property for an individual index of the array by using square brackets ([]) and specifying the index to be assigned within the square brackets.

array instance name {[index]}\* -> property name [= value];

Example 1

This example assigns a simple scalar.

```

reg {

field {} f1;

f1->name = "New name for Field 1";

} some_reg;

```

#### Example 2

This example assigns an array.

```

reg {

field {} f1;

f1->name = "New name for Field 1";

} some_reg[8];

some_reg->name = "This value is applied to all elements in the array";

some reg[3]->name = "Only applied to the 4th item in the array of 8";

```

#### 5.1.3.4 Property assignment precedence

There are several ways to set values on properties. The precedence for resolving them is (from highest to lowest priority):

- a) dynamic assignment (see 5.1.3.3)

- b) property assignment (see 5.1.3.1)

- c) default property assignment (see 5.1.3.2)

- d) SystemRDL default value for property type (see <u>Table 7</u>)

Example

```

reg {

default name ="def name";

field f_type { name = "other name"; };

field {} f1;

field { name = "property assigned name"; } f2;

f_type f3;

f3->name = "Dynamic Assignment";

} some reg;

```

#### Results

```

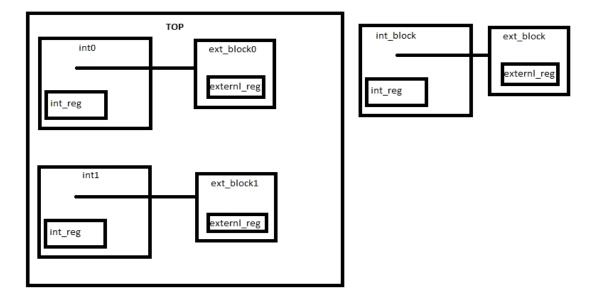

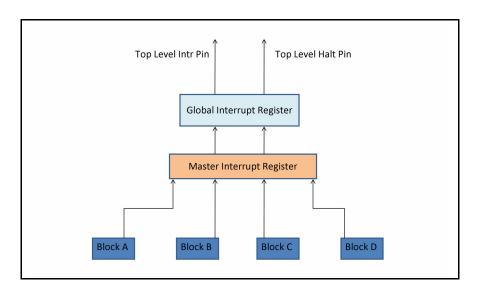

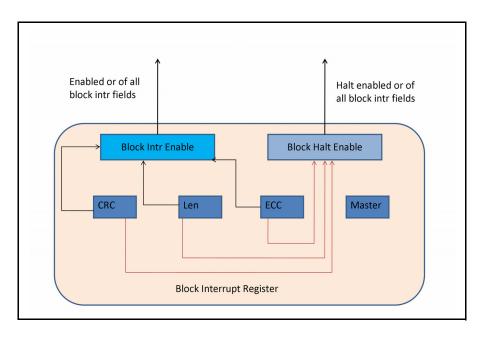

// Final Values of all fields